V821

来自Jack's Lab

(版本间的差异)

| (未显示1个用户的5个中间版本) | |||

| 第1行: | 第1行: | ||

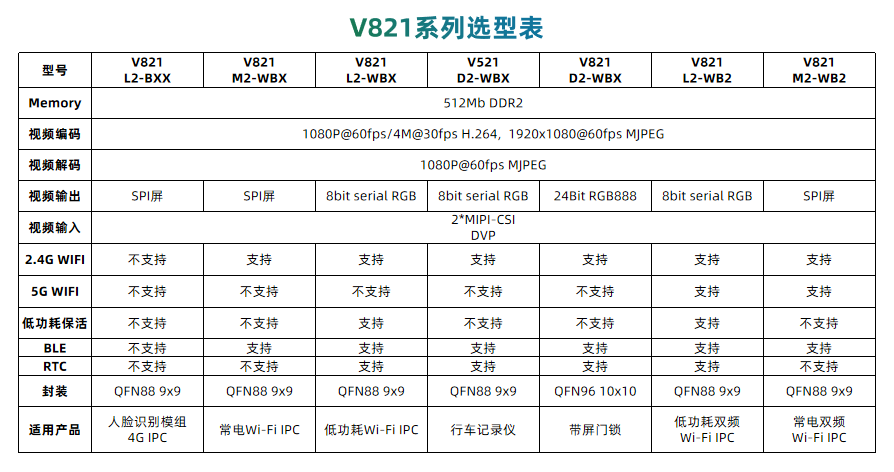

全志 2025 年推出,面向成本敏感的低功耗 AIoT 市场 | 全志 2025 年推出,面向成本敏感的低功耗 AIoT 市场 | ||

| − | 片内统一集成 64MB,有集成 2.4G/5G WiFi | + | 片内统一集成 64MB,有集成 2.4G/5G WiFi 的型号 |

[[文件:V821.png]] | [[文件:V821.png]] | ||

| 第9行: | 第9行: | ||

[[文件:V821-block.png]] | [[文件:V821-block.png]] | ||

| − | [[文件:V821-block2.png]] | + | * RISC-V CPU, up to 1.2GHz |

| + | ** 16KB l-cache、16KB D-cache、128KB L2 cache | ||

| + | ** 专用算子加速,支持 conv、depthwiseconv、maxpool、add、concat 等典型算子 | ||

| + | * RISC-V MCU, up to 600MHz | ||

| + | * 内置 64MB DDR2 SiP | ||

| + | * 可 SD2.0、eMMC4.41 和 SPI Flash (QUAD DTR 模式 SPI 接口) 启动 | ||

| + | * USB2.0 DRD x1,支持 UAC/UVC 协议 | ||

| + | * SPI x3,TWI x3,UART x4 | ||

| + | * 10/100Mbit/s RMIl x1 | ||

| + | * 12 通道 PWM,3 通道 GPADC | ||

| + | * Wi-Fi | ||

| + | ** 兼容 IEEE802.11b/g/n 标准 | ||

| + | ** 支持单频 2.4GHz 1T1R 模式 | ||

| + | ** 集成 LNA, PA 和 T/R 开关 | ||

| + | ** 安全支持 WPA/WPA2/WPA3-personal 和 WPS2.0 | ||

| + | ** 支持 STA、SoftAP、STA+SoftAP 和 Monitor 模式 | ||

| + | * 蓝牙 | ||

| + | ** 符合蓝牙低功耗 5.0 标准 | ||

| + | ** 支持数据传输速率:2Mbps、1Mbps、500Kbps 及 125Kbps | ||

| + | * ISP: 最大支持 3264x2448 分辨率 Sensor 接入 | ||

| + | * 支持 MIPI-CSI2 V1.1 和MIPI DPHY V1.0 标准,支持 2 个 1xlane 或 1 个 2xlane 的 MIPI CSI 接口,每通道最高速率 1.0Gbps | ||

| + | |||

| + | [[文件:V821-block2.png | 895px]] | ||

* QFN88 9x9mm, QFN96 10x10mm | * QFN88 9x9mm, QFN96 10x10mm | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == 硬件设计指南 == | ||

| + | |||

| + | https://docs.aw-ol.com/docs/soc/v821/hardware/v821_soc | ||

<br> | <br> | ||

2026年2月3日 (二) 10:22的最后版本

全志 2025 年推出,面向成本敏感的低功耗 AIoT 市场

片内统一集成 64MB,有集成 2.4G/5G WiFi 的型号

[编辑] 1 Overview

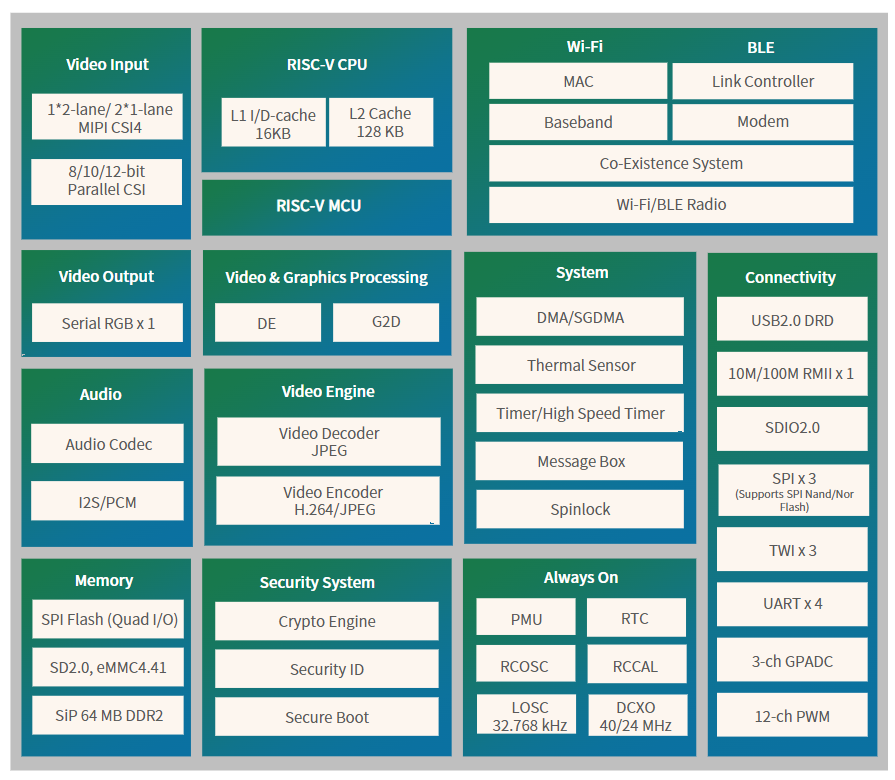

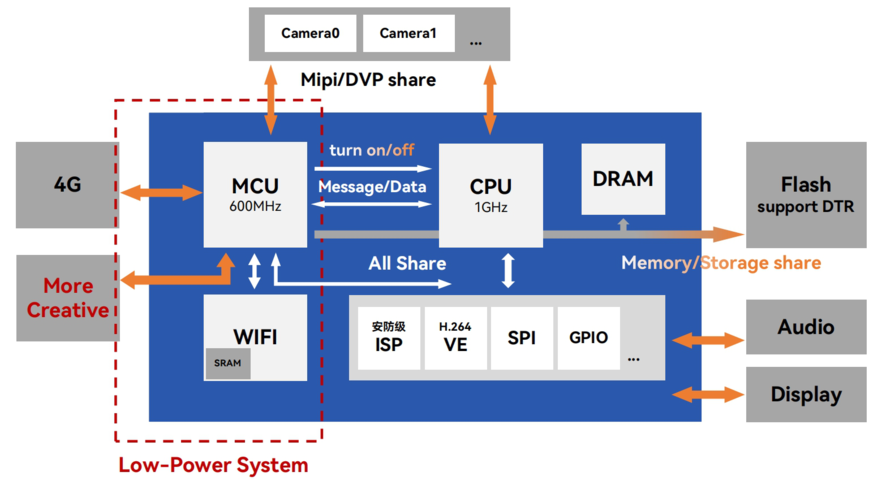

- RISC-V CPU, up to 1.2GHz

- 16KB l-cache、16KB D-cache、128KB L2 cache

- 专用算子加速,支持 conv、depthwiseconv、maxpool、add、concat 等典型算子

- RISC-V MCU, up to 600MHz

- 内置 64MB DDR2 SiP

- 可 SD2.0、eMMC4.41 和 SPI Flash (QUAD DTR 模式 SPI 接口) 启动

- USB2.0 DRD x1,支持 UAC/UVC 协议

- SPI x3,TWI x3,UART x4

- 10/100Mbit/s RMIl x1

- 12 通道 PWM,3 通道 GPADC

- Wi-Fi

- 兼容 IEEE802.11b/g/n 标准

- 支持单频 2.4GHz 1T1R 模式

- 集成 LNA, PA 和 T/R 开关

- 安全支持 WPA/WPA2/WPA3-personal 和 WPS2.0

- 支持 STA、SoftAP、STA+SoftAP 和 Monitor 模式

- 蓝牙

- 符合蓝牙低功耗 5.0 标准

- 支持数据传输速率:2Mbps、1Mbps、500Kbps 及 125Kbps

- ISP: 最大支持 3264x2448 分辨率 Sensor 接入

- 支持 MIPI-CSI2 V1.1 和MIPI DPHY V1.0 标准,支持 2 个 1xlane 或 1 个 2xlane 的 MIPI CSI 接口,每通道最高速率 1.0Gbps

- QFN88 9x9mm, QFN96 10x10mm

[编辑] 2 硬件设计指南

https://docs.aw-ol.com/docs/soc/v821/hardware/v821_soc