ESP32 RTC

(→rtc_pads_muxsel) |

(→RTC GPIO) |

||

| (未显示1个用户的100个中间版本) | |||

| 第1行: | 第1行: | ||

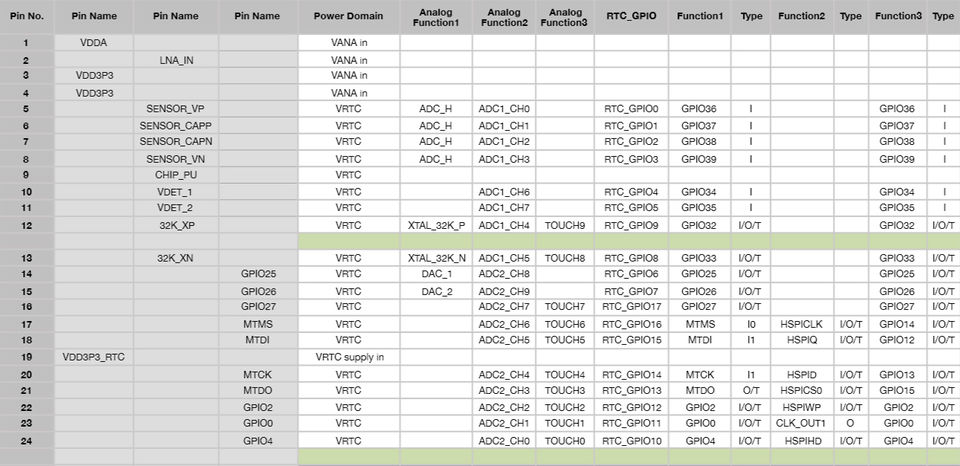

| − | == | + | == RTC GPIO == |

| − | + | RTC_GPIO0 ~ RTC_GPIO17 | |

| − | + | [[文件:Esp32-pin-adc.jpg | 960px]] | |

| − | + | {| border="0" width=89% cellspacing="1" cellpadding="5" align="center" bgcolor=#0066bb | |

| + | | style="background:#eeeeee" width=50| Pin NO. | ||

| + | | style="background:#eeeeee" | Pin Name | ||

| + | | style="background:#eeeeee" | RTC_GPIO | ||

| + | | style="background:#eeeeee" | Control Register | ||

| + | | style="background:#eeeeee" | MUX Bits | ||

| + | | style="background:#eeeeee" | After Reset | ||

| + | | style="background:#eeeeee" | Notes | ||

| + | |- | ||

| + | | style="background:#ffffff" | 5 | ||

| + | | style="background:#ffffff" | SENSOR_VP | ||

| + | | style="background:#ffffff" | RTC_GPIO0 | ||

| + | | style="background:#ffffff" | RTC_IO_SENSOR_PADS_REG | ||

| + | | style="background:#ffffff" | SENSE1_MUX_SEL, BIT[27] | ||

| + | | style="background:#ffffff" | 0 (Route to digital IO_MUX) | ||

| + | | style="background:#ffffff" | Only Input | ||

| + | |- | ||

| + | | style="background:#ffffff" | 6 | ||

| + | | style="background:#ffffff" | SENSOR_CAPP | ||

| + | | style="background:#ffffff" | RTC_GPIO1 | ||

| + | | style="background:#ffffff" | RTC_IO_SENSOR_PADS_REG | ||

| + | | style="background:#ffffff" | SENSE1_MUX_SEL, BIT[26] | ||

| + | | style="background:#ffffff" | 0 | ||

| + | | style="background:#ffffff" | Only Input | ||

| + | |- | ||

| + | | style="background:#ffffff" | 7 | ||

| + | | style="background:#ffffff" | SENSOR_CAPN | ||

| + | | style="background:#ffffff" | RTC_GPIO2 | ||

| + | | style="background:#ffffff" | RTC_IO_SENSOR_PADS_REG | ||

| + | | style="background:#ffffff" | SENSE3_MUX_SEL, BIT[25] | ||

| + | | style="background:#ffffff" | 0 | ||

| + | | style="background:#ffffff" | Only Input | ||

| + | |- | ||

| + | | style="background:#ffffff" | 8 | ||

| + | | style="background:#ffffff" | SENSOR_VN | ||

| + | | style="background:#ffffff" | RTC_GPIO3 | ||

| + | | style="background:#ffffff" | RTC_IO_SENSOR_PADS_REG | ||

| + | | style="background:#ffffff" | SENSE4_MUX_SEL, BIT[24] | ||

| + | | style="background:#ffffff" | 0 | ||

| + | | style="background:#ffffff" | Only Input | ||

| + | |- | ||

| + | | style="background:#ffffff" | 10 | ||

| + | | style="background:#ffffff" | VDET_1 | ||

| + | | style="background:#ffffff" | RTC_GPIO4 | ||

| + | | style="background:#ffffff" | RTC_IO_ADC_PAD_REG | ||

| + | | style="background:#ffffff" | ADC1_MUX_SEL, BIT[29] | ||

| + | | style="background:#ffffff" | 0 | ||

| + | | style="background:#ffffff" | Only Input | ||

| + | |- | ||

| + | | style="background:#ffffff" | 11 | ||

| + | | style="background:#ffffff" | VDET_2 | ||

| + | | style="background:#ffffff" | RTC_GPIO5 | ||

| + | | style="background:#ffffff" | RTC_IO_ADC_PAD_REG | ||

| + | | style="background:#ffffff" | ADC2_MUX_SEL, BIT[28] | ||

| + | | style="background:#ffffff" | 0 | ||

| + | | style="background:#ffffff" | Only Input | ||

| + | |- | ||

| + | | style="background:#ffffff" | 12 | ||

| + | | style="background:#ffffff" | 32K_XP | ||

| + | | style="background:#ffffff" | RTC_GPIO9 | ||

| + | | style="background:#ffffff" | RTC_IO_XTAL_32K_PAD_REG | ||

| + | | style="background:#ffffff" | X32P_MUX_SEL, BIT[17] | ||

| + | | style="background:#ffffff" | 0 (Route to digital IO_MUX) | ||

| + | | style="background:#ffffff" | Set to 1 by esp-idf, route to RTC | ||

| + | |- | ||

| + | | style="background:#ffffff" | 13 | ||

| + | | style="background:#ffffff" | 32K_XN | ||

| + | | style="background:#ffffff" | RTC_GPIO8 | ||

| + | | style="background:#ffffff" | RTC_IO_XTAL_32K_PAD_REG | ||

| + | | style="background:#ffffff" | X32N_MUX_SEL, BIT[18] | ||

| + | | style="background:#ffffff" | 0 (Route to digital IO_MUX) | ||

| + | | style="background:#ffffff" | Set to 1 by esp-idf, route to RTC | ||

| + | |- | ||

| + | | style="background:#ffffff" | 14 | ||

| + | | style="background:#ffffff" | DAC_1 | ||

| + | | style="background:#ffffff" | RTC_GPIO6 | ||

| + | | style="background:#ffffff" | RTC_IO_PAD_DAC1_REG | ||

| + | | style="background:#ffffff" | PDAC1_MUX_SEL, BIT[17] | ||

| + | | style="background:#ffffff" | 0 | ||

| + | | style="background:#ffffff" | | ||

| + | |- | ||

| + | | style="background:#ffffff" | 15 | ||

| + | | style="background:#ffffff" | DAC_2 | ||

| + | | style="background:#ffffff" | RTC_GPIO7 | ||

| + | | style="background:#ffffff" | RTC_IO_PAD_DAC2_REG | ||

| + | | style="background:#ffffff" | PDAC2_MUX_SEL, BIT[17] | ||

| + | | style="background:#ffffff" | 0 | ||

| + | | style="background:#ffffff" | | ||

| + | |- | ||

| + | | style="background:#ffffff" | 16 ~ 24 | ||

| + | | style="background:#ffffff" | TOUCH7 ~ TOUCH0 | ||

| + | | style="background:#ffffff" | RTC_GPIO17 ~ 10 | ||

| + | | style="background:#ffffff" | TOUCH_PADn_REG (n = 7 ~ 0) | ||

| + | | style="background:#ffffff" | PADn_TO_GPIO, BIT[19] | ||

| + | | style="background:#ffffff" | 0 (Route to RTC domain) | ||

| + | | style="background:#ffffff" | | ||

| + | |- | ||

| + | | style="background:#ffffff" | | ||

| + | | style="background:#ffffff" | | ||

| + | | style="background:#ffffff" | | ||

| + | | style="background:#ffffff" | | ||

| + | | style="background:#ffffff" | | ||

| + | | style="background:#ffffff" | | ||

| + | | style="background:#ffffff" | | ||

| + | |} | ||

| − | |||

| − | + | You need to clear the following bits if you want to use the GPIO32 and GPIO33 as the general GPIO: | |

| − | + | <pre> | |

| + | REG_CLR_BIT(RTC_IO_XTAL_32K_PAD_REG, RTC_IO_X32P_MUX_SEL); /* gpio32 route to digital io_mux */ | ||

| + | REG_CLR_BIT(RTC_IO_XTAL_32K_PAD_REG, RTC_IO_X32N_MUX_SEL); /* gpio33 route to digital io_mux */ | ||

| + | </pre> | ||

<br><br> | <br><br> | ||

| 第176行: | 第282行: | ||

#define RTC_CNTL_DATE_REG (DR_REG_RTCCNTL_BASE + 0x13c) | #define RTC_CNTL_DATE_REG (DR_REG_RTCCNTL_BASE + 0x13c) | ||

</source> | </source> | ||

| + | |||

| + | <br><br> | ||

| + | |||

| + | == Memory == | ||

| + | |||

| + | === FAST Memory === | ||

| + | |||

| + | RTC FAST Memory 为 8 KB SRAM,其只能被 PRO_CPU 通过数据总线 0x3FF8_0000 ~ 0x3FF8_1FFF 读写,或被 PRO_CPU 通过指令总线 0x400C_0000~0x400C_1FFF 读写。与其他存储器不同,APP_CPU 不能访问 RTC FAST Memory | ||

| + | |||

| + | |||

| + | PRO_CPU 的这两段地址同序访问 RTC FAST Memory。即地址 0x3FF8_0000 与 0x400C_0000 访问到相同的 word,0x3FF8_0004与0x400C_0004访问到相同的word,0x3FF8_0008与0x400C_0008访问到相同的word, 以此类推。APP_CPU 的这两段地址不能访问到 RTC FAST Memory,也不能访问到其他任何目标 | ||

| + | |||

| + | <br><br> | ||

| + | |||

| + | === SLOW Memory === | ||

| + | |||

| + | RTC SLOW Memory 为 8 KB SRAM,其可以被两个 CPU 通过数据总线与指令总线共用地址段 0x5000_0000 ~ 0x5000_1FFF 读写。 | ||

<br><br> | <br><br> | ||

== Power Consumption == | == Power Consumption == | ||

| + | |||

| + | '''Light Sleep Mode:''' | ||

| + | |||

| + | * The CPU is paused | ||

| + | * WiFi/BT base-band and radio are Off | ||

| + | * The RTC and ULP are running | ||

| + | * Any wake-up events (MAC, host, RTC timer, or external interrupts) will wake up the chip | ||

| + | * Current consumption is 800uA | ||

| + | |||

'''We are care of Deep-Sleep mode:''' | '''We are care of Deep-Sleep mode:''' | ||

| 第196行: | 第328行: | ||

* Power Consumption: 2.5uA | * Power Consumption: 2.5uA | ||

| + | |||

| + | <br> | ||

| + | |||

| + | === Registers === | ||

| + | |||

| + | <source lang=c> | ||

| + | #define RTC_CNTL_REG (DR_REG_RTCCNTL_BASE + 0x7c) | ||

| + | /* RTC_CNTL_FORCE_PU : R/W ;bitpos:[31] ;default: 1'd1 ; */ | ||

| + | /*description: RTC_REG force power up*/ | ||

| + | #define RTC_CNTL_FORCE_PU_S 31 | ||

| + | /* RTC_CNTL_FORCE_PD : R/W ;bitpos:[30] ;default: 1'd0 ; */ | ||

| + | /*description: RTC_REG force power down (for RTC_REG power down means decrease | ||

| + | the voltage to 0.8v or lower )*/ | ||

| + | #define RTC_CNTL_FORCE_PD_S 30 | ||

| + | /* RTC_CNTL_DBOOST_FORCE_PU : R/W ;bitpos:[29] ;default: 1'd1 ; */ | ||

| + | /*description: RTC_DBOOST force power up*/ | ||

| + | #define RTC_CNTL_DBOOST_FORCE_PU_S 29 | ||

| + | /* RTC_CNTL_DBOOST_FORCE_PD : R/W ;bitpos:[28] ;default: 1'd0 ; */ | ||

| + | /*description: RTC_DBOOST force power down*/ | ||

| + | #define RTC_CNTL_DBOOST_FORCE_PD_S 28 | ||

| + | /* RTC_CNTL_DBIAS_WAK : R/W ;bitpos:[27:25] ;default: 3'd4 ; */ | ||

| + | /*description: RTC_DBIAS during wakeup*/ | ||

| + | #define RTC_CNTL_DBIAS_WAK_S 25 | ||

| + | /* RTC_CNTL_DBIAS_SLP : R/W ;bitpos:[24:22] ;default: 3'd4 ; */ | ||

| + | /*description: RTC_DBIAS during sleep*/ | ||

| + | #define RTC_CNTL_DBIAS_SLP_S 22 | ||

| + | /* RTC_CNTL_SCK_DCAP : R/W ;bitpos:[21:14] ;default: 8'd0 ; */ | ||

| + | /*description: SCK_DCAP*/ | ||

| + | #define RTC_CNTL_SCK_DCAP_S 14 | ||

| + | /* RTC_CNTL_DIG_DBIAS_WAK : R/W ;bitpos:[13:11] ;default: 3'd4 ; */ | ||

| + | /*description: DIG_REG_DBIAS during wakeup*/ | ||

| + | #define RTC_CNTL_DIG_DBIAS_WAK_S 11 | ||

| + | /* RTC_CNTL_DIG_DBIAS_SLP : R/W ;bitpos:[10:8] ;default: 3'd4 ; */ | ||

| + | /*description: DIG_REG_DBIAS during sleep*/ | ||

| + | #define RTC_CNTL_DIG_DBIAS_SLP_S 8 | ||

| + | /* RTC_CNTL_SCK_DCAP_FORCE : R/W ;bitpos:[7] ;default: 1'd0 ; */ | ||

| + | /*description: N/A*/ | ||

| + | #define RTC_CNTL_SCK_DCAP_FORCE_S 7 | ||

| + | |||

| + | |||

| + | #define RTC_CNTL_PWC_REG (DR_REG_RTCCNTL_BASE + 0x80) | ||

| + | /* RTC_CNTL_PD_EN : R/W ;bitpos:[20] ;default: 1'd0 ; */ | ||

| + | /*description: enable power down rtc_peri in sleep*/ | ||

| + | #define RTC_CNTL_PD_EN_S 20 | ||

| + | /* RTC_CNTL_FORCE_PU : R/W ;bitpos:[19] ;default: 1'd0 ; */ | ||

| + | /*description: rtc_peri force power up*/ | ||

| + | #define RTC_CNTL_PWC_FORCE_PU_S 19 | ||

| + | /* RTC_CNTL_FORCE_PD : R/W ;bitpos:[18] ;default: 1'b0 ; */ | ||

| + | /*description: rtc_peri force power down*/ | ||

| + | #define RTC_CNTL_PWC_FORCE_PD_S 18 | ||

| + | /* RTC_CNTL_SLOWMEM_PD_EN : R/W ;bitpos:[17] ;default: 1'b0 ; */ | ||

| + | /*description: enable power down RTC memory in sleep*/ | ||

| + | #define RTC_CNTL_SLOWMEM_PD_EN_S 17 | ||

| + | /* RTC_CNTL_SLOWMEM_FORCE_PU : R/W ;bitpos:[16] ;default: 1'b1 ; */ | ||

| + | /*description: RTC memory force power up*/ | ||

| + | #define RTC_CNTL_SLOWMEM_FORCE_PU_S 16 | ||

| + | /* RTC_CNTL_SLOWMEM_FORCE_PD : R/W ;bitpos:[15] ;default: 1'b0 ; */ | ||

| + | /*description: RTC memory force power down*/ | ||

| + | #define RTC_CNTL_SLOWMEM_FORCE_PD_S 15 | ||

| + | /* RTC_CNTL_FASTMEM_PD_EN : R/W ;bitpos:[14] ;default: 1'b0 ; */ | ||

| + | /*description: enable power down fast RTC memory in sleep*/ | ||

| + | #define RTC_CNTL_FASTMEM_PD_EN_S 14 | ||

| + | /* RTC_CNTL_FASTMEM_FORCE_PU : R/W ;bitpos:[13] ;default: 1'b1 ; */ | ||

| + | /*description: Fast RTC memory force power up*/ | ||

| + | #define RTC_CNTL_FASTMEM_FORCE_PU_S 13 | ||

| + | /* RTC_CNTL_FASTMEM_FORCE_PD : R/W ;bitpos:[12] ;default: 1'b0 ; */ | ||

| + | /*description: Fast RTC memory force power down*/ | ||

| + | #define RTC_CNTL_FASTMEM_FORCE_PD_S 12 | ||

| + | /* RTC_CNTL_SLOWMEM_FORCE_LPU : R/W ;bitpos:[11] ;default: 1'b1 ; */ | ||

| + | /*description: RTC memory force no PD*/ | ||

| + | #define RTC_CNTL_SLOWMEM_FORCE_LPU_S 11 | ||

| + | /* RTC_CNTL_SLOWMEM_FORCE_LPD : R/W ;bitpos:[10] ;default: 1'b0 ; */ | ||

| + | /*description: RTC memory force PD*/ | ||

| + | #define RTC_CNTL_SLOWMEM_FORCE_LPD_S 10 | ||

| + | /* RTC_CNTL_SLOWMEM_FOLW_CPU : R/W ;bitpos:[9] ;default: 1'b0 ; */ | ||

| + | /*description: 1: RTC memory PD following CPU 0: RTC memory PD following RTC state machine*/ | ||

| + | #define RTC_CNTL_SLOWMEM_FOLW_CPU_S 9 | ||

| + | /* RTC_CNTL_FASTMEM_FORCE_LPU : R/W ;bitpos:[8] ;default: 1'b1 ; */ | ||

| + | /*description: Fast RTC memory force no PD*/ | ||

| + | #define RTC_CNTL_FASTMEM_FORCE_LPU_S 8 | ||

| + | /* RTC_CNTL_FASTMEM_FORCE_LPD : R/W ;bitpos:[7] ;default: 1'b0 ; */ | ||

| + | /*description: Fast RTC memory force PD*/ | ||

| + | #define RTC_CNTL_FASTMEM_FORCE_LPD_S 7 | ||

| + | /* RTC_CNTL_FASTMEM_FOLW_CPU : R/W ;bitpos:[6] ;default: 1'b0 ; */ | ||

| + | /*description: 1: Fast RTC memory PD following CPU 0: fast RTC memory PD following | ||

| + | RTC state machine*/ | ||

| + | #define RTC_CNTL_FASTMEM_FOLW_CPU_S 6 | ||

| + | /* RTC_CNTL_FORCE_NOISO : R/W ;bitpos:[5] ;default: 1'd1 ; */ | ||

| + | /*description: rtc_peri force no ISO*/ | ||

| + | #define RTC_CNTL_FORCE_NOISO_S 5 | ||

| + | /* RTC_CNTL_FORCE_ISO : R/W ;bitpos:[4] ;default: 1'd0 ; */ | ||

| + | /*description: rtc_peri force ISO*/ | ||

| + | #define RTC_CNTL_FORCE_ISO_S 4 | ||

| + | /* RTC_CNTL_SLOWMEM_FORCE_ISO : R/W ;bitpos:[3] ;default: 1'b0 ; */ | ||

| + | /*description: RTC memory force ISO*/ | ||

| + | #define RTC_CNTL_SLOWMEM_FORCE_ISO_S 3 | ||

| + | /* RTC_CNTL_SLOWMEM_FORCE_NOISO : R/W ;bitpos:[2] ;default: 1'b1 ; */ | ||

| + | /*description: RTC memory force no ISO*/ | ||

| + | #define RTC_CNTL_SLOWMEM_FORCE_NOISO_S 2 | ||

| + | /* RTC_CNTL_FASTMEM_FORCE_ISO : R/W ;bitpos:[1] ;default: 1'b0 ; */ | ||

| + | /*description: Fast RTC memory force ISO*/ | ||

| + | #define RTC_CNTL_FASTMEM_FORCE_ISO_S 1 | ||

| + | /* RTC_CNTL_FASTMEM_FORCE_NOISO : R/W ;bitpos:[0] ;default: 1'b1 ; */ | ||

| + | /*description: Fast RTC memory force no ISO*/ | ||

| + | #define RTC_CNTL_FASTMEM_FORCE_NOISO_S 0 | ||

| + | </source> | ||

<br><br> | <br><br> | ||

| 第209行: | 第447行: | ||

* Internal 31.25KHz clock (derived from the internal 8MHz oscillator divided by 256) | * Internal 31.25KHz clock (derived from the internal 8MHz oscillator divided by 256) | ||

| + | <br> | ||

| + | |||

| + | === API === | ||

| + | |||

| + | ==== rtc_set_fast_freq ==== | ||

| + | |||

| + | <source lang=bash> | ||

| + | 0x4008f87c <rtc_set_fast_freq>: entry a1, 32 | ||

| + | 0x4008f87f <rtc_set_fast_freq+3>: l32r a8, 0x4008e53c /* a8 = *(0x4008e53c) = 0x3ff48070, RTC_CNTL_CLK_CONF_REG */ | ||

| + | 0x4008f882 <rtc_set_fast_freq+6>: l32r a11, 0x40086318 /* a11 = *(0x40086318) = 0xdfffffff, BIT(29), fast_clk_rtc sel */ | ||

| + | 0x4008f885 <rtc_set_fast_freq+9>: memw | ||

| + | 0x4008f888 <rtc_set_fast_freq+12>: l32i.n a9, a8, 0 /* a9 = read RTC_CNTL_CLK_CONF_REG */ | ||

| + | 0x4008f88a <rtc_set_fast_freq+14>: extui a2, a2, 0, 1 /* a2 = p1[0] */ | ||

| + | 0x4008f88d <rtc_set_fast_freq+17>: slli a10, a2, 29 /* a10 = p1[0] << 29 */ | ||

| + | 0x4008f890 <rtc_set_fast_freq+20>: and a9, a9, a11 | ||

| + | 0x4008f893 <rtc_set_fast_freq+23>: or a9, a10, a9 /* a9 = RTC_CNTL_CLK_CONF_REG & 0xdfffffff | (p1[0] << 29) | ||

| + | 0x4008f896 <rtc_set_fast_freq+26>: memw | ||

| + | 0x4008f899 <rtc_set_fast_freq+29>: s32i.n a9, a8, 0 /* write to RTC_CNTL_CLK_CONF_REG */ | ||

| + | /* fast_clk_rtc sel. 0: XTAL div 4 1: CK8M */ | ||

| + | |||

| + | 0x4008f89b <rtc_set_fast_freq+31>: movi a10, 3 | ||

| + | 0x4008f89e <rtc_set_fast_freq+34>: l32r a8, 0x40080850 /* a8 = *(0x40080850) = 0x40008534, ets_delay_us */ | ||

| + | 0x4008f8a1 <rtc_set_fast_freq+37>: callx8 a8 /* ets_delay_us(3) */ | ||

| + | 0x4008f8a4 <rtc_set_fast_freq+40>: retw.n | ||

| + | </source> | ||

| + | |||

| + | So: | ||

| + | |||

| + | <source lang=c> | ||

| + | /* | ||

| + | * fast_clk_rtc_sel = 0: XTAL div 4 | ||

| + | * fast_clk_rtc_sel = 1: CK8M | ||

| + | */ | ||

| + | void rtc_set_fast_freq(uint8_t fast_clk_rtc_sel); | ||

| + | </source> | ||

| + | |||

| + | <br> | ||

| + | |||

| + | ==== rtc_set_slow_freq ==== | ||

| + | |||

| + | <source lang=bash> | ||

| + | 0x4008f854 <rtc_set_slow_freq>: entry a1, 32 | ||

| + | 0x4008f857 <rtc_set_slow_freq+3>: l32r a8, 0x4008e53c /* a8 = 0x3ff48070, RTC_CNTL_CLK_CONF_REG */ | ||

| + | 0x4008f85a <rtc_set_slow_freq+6>: l32r a10, 0x4008af18 /* a10 = 0x3fffffff, BIT[31:30] */ | ||

| + | 0x4008f85d <rtc_set_slow_freq+9>: memw | ||

| + | 0x4008f860 <rtc_set_slow_freq+12>: l32i.n a9, a8, 0 | ||

| + | 0x4008f862 <rtc_set_slow_freq+14>: slli a2, a2, 30 | ||

| + | 0x4008f865 <rtc_set_slow_freq+17>: and a9, a9, a10 | ||

| + | 0x4008f868 <rtc_set_slow_freq+20>: or a9, a2, a9 | ||

| + | 0x4008f86b <rtc_set_slow_freq+23>: memw | ||

| + | 0x4008f86e <rtc_set_slow_freq+26>: s32i.n a9, a8, 0 | ||

| + | |||

| + | 0x4008f870 <rtc_set_slow_freq+28>: movi a10, 0x12c /* a10 = 300 */ | ||

| + | 0x4008f873 <rtc_set_slow_freq+31>: l32r a8, 0x40080850 | ||

| + | 0x4008f876 <rtc_set_slow_freq+34>: callx8 a8 /* ets_delay_us(300) */ | ||

| + | 0x4008f879 <rtc_set_slow_freq+37>: retw.n | ||

| + | </source> | ||

| + | |||

| + | So: | ||

| + | |||

| + | <source lang=c> | ||

| + | /* | ||

| + | * slow_clk_rtc_sel = 0: SLOW_CK | ||

| + | * slow_clk_rtc_sel = 1: CK_XTAL_32K | ||

| + | * slow_clk_rtc_sel = 2: CK8M_D256_OUT | ||

| + | */ | ||

| + | void rtc_set_slow_freq(uint8_t slow_clk_rtc_sel); | ||

| + | </source> | ||

| + | |||

| + | <br> | ||

| + | |||

| + | ==== rtc_xtal_32k_ena ==== | ||

| + | |||

| + | <source lang=c> | ||

| + | void rtc_xtal_32k_ena(uint8_t enabled); | ||

| + | </source> | ||

| + | |||

| + | more details please refer to: [http://wiki.jackslab.org/ESP32_Smoke_Detector#0x4008f5f4 RTC XTAL 32K enable] | ||

| + | |||

| + | <br> | ||

| + | |||

| + | ==== rtc_init_clk_lite ==== | ||

| + | |||

| + | <source lang=c> | ||

| + | void rtc_init_clk_lite(uint32_t st) | ||

| + | { | ||

| + | rtc_init_clk(st, 1, 0, 0, 255, 172); | ||

| + | } | ||

| + | </source> | ||

| + | |||

| + | More details please refer to: [http://wiki.jackslab.org/ESP32_Smoke_Detector#rtc_init_clk_lite RTC Init Clock Lite] | ||

| + | |||

| + | <br> | ||

| + | |||

| + | ==== rtc_init_clk ==== | ||

| + | |||

| + | <source lang=c> | ||

| + | void rtc_init_clk(uint32_t st, uint8_t fast_clk_sel, uint8_t ck8m_divider, | ||

| + | uint8_t slow_clk_sel,uint8_t sck_dcap,uint8_t ck8_dfreq); | ||

| + | |||

| + | rtc_init_clk(0, 1, 0, 0, 255, 172); | ||

| + | </source> | ||

| + | |||

| + | More details please refer to: [http://wiki.jackslab.org/ESP32_Smoke_Detector#rtc_init_clk RTC Init Clock] | ||

| + | |||

| + | <br> | ||

| − | + | === Register === | |

<source lang=cpp> | <source lang=cpp> | ||

| 第216行: | 第560行: | ||

/* RTC_CNTL_ANA_CLK_RTC_SEL : R/W ;bitpos:[31:30] ;default: 2'd0 ; */ | /* RTC_CNTL_ANA_CLK_RTC_SEL : R/W ;bitpos:[31:30] ;default: 2'd0 ; */ | ||

/*description: slow_clk_rtc sel. 0: SLOW_CK 1: CK_XTAL_32K 2: CK8M_D256_OUT*/ | /*description: slow_clk_rtc sel. 0: SLOW_CK 1: CK_XTAL_32K 2: CK8M_D256_OUT*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_ANA_CLK_RTC_SEL_S 30 | #define RTC_CNTL_ANA_CLK_RTC_SEL_S 30 | ||

/* RTC_CNTL_FAST_CLK_RTC_SEL : R/W ;bitpos:[29] ;default: 1'b0 ; */ | /* RTC_CNTL_FAST_CLK_RTC_SEL : R/W ;bitpos:[29] ;default: 1'b0 ; */ | ||

/*description: fast_clk_rtc sel. 0: XTAL div 4 1: CK8M*/ | /*description: fast_clk_rtc sel. 0: XTAL div 4 1: CK8M*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_FAST_CLK_RTC_SEL_S 29 | #define RTC_CNTL_FAST_CLK_RTC_SEL_S 29 | ||

/* RTC_CNTL_SOC_CLK_SEL : R/W ;bitpos:[28:27] ;default: 2'd0 ; */ | /* RTC_CNTL_SOC_CLK_SEL : R/W ;bitpos:[28:27] ;default: 2'd0 ; */ | ||

/*description: SOC clock sel. 0: XTAL 1: PLL 2: CK8M 3: APLL*/ | /*description: SOC clock sel. 0: XTAL 1: PLL 2: CK8M 3: APLL*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_SOC_CLK_SEL_S 27 | #define RTC_CNTL_SOC_CLK_SEL_S 27 | ||

/* RTC_CNTL_CK8M_FORCE_PU : R/W ;bitpos:[26] ;default: 1'd0 ; */ | /* RTC_CNTL_CK8M_FORCE_PU : R/W ;bitpos:[26] ;default: 1'd0 ; */ | ||

/*description: CK8M force power up*/ | /*description: CK8M force power up*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_CK8M_FORCE_PU_S 26 | #define RTC_CNTL_CK8M_FORCE_PU_S 26 | ||

/* RTC_CNTL_CK8M_FORCE_PD : R/W ;bitpos:[25] ;default: 1'd0 ; */ | /* RTC_CNTL_CK8M_FORCE_PD : R/W ;bitpos:[25] ;default: 1'd0 ; */ | ||

/*description: CK8M force power down*/ | /*description: CK8M force power down*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_CK8M_FORCE_PD_S 25 | #define RTC_CNTL_CK8M_FORCE_PD_S 25 | ||

/* RTC_CNTL_CK8M_DFREQ : R/W ;bitpos:[24:17] ;default: 8'd0 ; */ | /* RTC_CNTL_CK8M_DFREQ : R/W ;bitpos:[24:17] ;default: 8'd0 ; */ | ||

/*description: CK8M_DFREQ*/ | /*description: CK8M_DFREQ*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_CK8M_DFREQ_S 17 | #define RTC_CNTL_CK8M_DFREQ_S 17 | ||

/* RTC_CNTL_CK8M_FORCE_NOGATING : R/W ;bitpos:[16] ;default: 1'd0 ; */ | /* RTC_CNTL_CK8M_FORCE_NOGATING : R/W ;bitpos:[16] ;default: 1'd0 ; */ | ||

/*description: CK8M force no gating during sleep*/ | /*description: CK8M force no gating during sleep*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_CK8M_FORCE_NOGATING_S 16 | #define RTC_CNTL_CK8M_FORCE_NOGATING_S 16 | ||

/* RTC_CNTL_XTAL_FORCE_NOGATING : R/W ;bitpos:[15] ;default: 1'd0 ; */ | /* RTC_CNTL_XTAL_FORCE_NOGATING : R/W ;bitpos:[15] ;default: 1'd0 ; */ | ||

/*description: XTAL force no gating during sleep*/ | /*description: XTAL force no gating during sleep*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_XTAL_FORCE_NOGATING_S 15 | #define RTC_CNTL_XTAL_FORCE_NOGATING_S 15 | ||

/* RTC_CNTL_CK8M_DIV_SEL : R/W ;bitpos:[14:12] ;default: 3'd2 ; */ | /* RTC_CNTL_CK8M_DIV_SEL : R/W ;bitpos:[14:12] ;default: 3'd2 ; */ | ||

/*description: divider = reg_ck8m_div_sel + 1*/ | /*description: divider = reg_ck8m_div_sel + 1*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_CK8M_DIV_SEL_S 12 | #define RTC_CNTL_CK8M_DIV_SEL_S 12 | ||

/* RTC_CNTL_CK8M_DFREQ_FORCE : R/W ;bitpos:[11] ;default: 1'd0 ; */ | /* RTC_CNTL_CK8M_DFREQ_FORCE : R/W ;bitpos:[11] ;default: 1'd0 ; */ | ||

/*description: */ | /*description: */ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_CK8M_DFREQ_FORCE_S 11 | #define RTC_CNTL_CK8M_DFREQ_FORCE_S 11 | ||

/* RTC_CNTL_DIG_CLK8M_EN : R/W ;bitpos:[10] ;default: 1'd0 ; */ | /* RTC_CNTL_DIG_CLK8M_EN : R/W ;bitpos:[10] ;default: 1'd0 ; */ | ||

/*description: enable CK8M for digital core (no relationship with RTC core)*/ | /*description: enable CK8M for digital core (no relationship with RTC core)*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_DIG_CLK8M_EN_S 10 | #define RTC_CNTL_DIG_CLK8M_EN_S 10 | ||

/* RTC_CNTL_DIG_CLK8M_D256_EN : R/W ;bitpos:[9] ;default: 1'd1 ; */ | /* RTC_CNTL_DIG_CLK8M_D256_EN : R/W ;bitpos:[9] ;default: 1'd1 ; */ | ||

/*description: enable CK8M_D256_OUT for digital core (no relationship with RTC core)*/ | /*description: enable CK8M_D256_OUT for digital core (no relationship with RTC core)*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_DIG_CLK8M_D256_EN_S 9 | #define RTC_CNTL_DIG_CLK8M_D256_EN_S 9 | ||

/* RTC_CNTL_DIG_XTAL32K_EN : R/W ;bitpos:[8] ;default: 1'd0 ; */ | /* RTC_CNTL_DIG_XTAL32K_EN : R/W ;bitpos:[8] ;default: 1'd0 ; */ | ||

/*description: enable CK_XTAL_32K for digital core (no relationship with RTC core)*/ | /*description: enable CK_XTAL_32K for digital core (no relationship with RTC core)*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_DIG_XTAL32K_EN_S 8 | #define RTC_CNTL_DIG_XTAL32K_EN_S 8 | ||

/* RTC_CNTL_ENB_CK8M_DIV : R/W ;bitpos:[7] ;default: 1'd0 ; */ | /* RTC_CNTL_ENB_CK8M_DIV : R/W ;bitpos:[7] ;default: 1'd0 ; */ | ||

/*description: 1: CK8M_D256_OUT is actually CK8M 0: CK8M_D256_OUT is CK8M divided by 256*/ | /*description: 1: CK8M_D256_OUT is actually CK8M 0: CK8M_D256_OUT is CK8M divided by 256*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_ENB_CK8M_DIV_S 7 | #define RTC_CNTL_ENB_CK8M_DIV_S 7 | ||

/* RTC_CNTL_ENB_CK8M : R/W ;bitpos:[6] ;default: 1'd0 ; */ | /* RTC_CNTL_ENB_CK8M : R/W ;bitpos:[6] ;default: 1'd0 ; */ | ||

/*description: disable CK8M and CK8M_D256_OUT*/ | /*description: disable CK8M and CK8M_D256_OUT*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_ENB_CK8M_S 6 | #define RTC_CNTL_ENB_CK8M_S 6 | ||

/* RTC_CNTL_CK8M_DIV : R/W ;bitpos:[5:4] ;default: 2'b01 ; */ | /* RTC_CNTL_CK8M_DIV : R/W ;bitpos:[5:4] ;default: 2'b01 ; */ | ||

/*description: CK8M_D256_OUT divider. 00: div128 01: div256 10: div512 11: div1024.*/ | /*description: CK8M_D256_OUT divider. 00: div128 01: div256 10: div512 11: div1024.*/ | ||

| − | |||

| − | |||

| − | |||

#define RTC_CNTL_CK8M_DIV_S 4 | #define RTC_CNTL_CK8M_DIV_S 4 | ||

#define RTC_IO_XTAL_32K_PAD_REG (DR_REG_RTCIO_BASE + 0x8c) | #define RTC_IO_XTAL_32K_PAD_REG (DR_REG_RTCIO_BASE + 0x8c) | ||

| + | /* e.g. 0x84160018 */ | ||

| + | /* RTC_IO_XPD_XTAL_32K : R/W ;bitpos:[19] ;default: 1'd0 ; */ | ||

| + | /*description: Power up 32kHz crystal oscillator*/ | ||

| + | #define RTC_IO_XPD_XTAL_32K_S 19 | ||

| + | /* RTC_IO_X32N_MUX_SEL : R/W ;bitpos:[18] ;default: 1'd0 ; */ | ||

| + | /*description: Ò1Ó select the digital function Ó0Óslection the rtc function*/ | ||

| + | #define RTC_IO_X32N_MUX_SEL_S 18 | ||

| + | /* RTC_IO_X32P_MUX_SEL : R/W ;bitpos:[17] ;default: 1'd0 ; */ | ||

| + | /*description: Ò1Ó select the digital function Ó0Óslection the rtc function*/ | ||

| + | #define RTC_IO_X32P_MUX_SEL_S 17 | ||

| + | /* RTC_IO_X32N_FUN_SEL : R/W ;bitpos:[16:15] ;default: 2'd0 ; */ | ||

| + | /*description: the functional selection signal of the pad*/ | ||

| + | #define RTC_IO_X32N_FUN_SEL_S 15 | ||

| + | /* RTC_IO_X32P_FUN_SEL : R/W ;bitpos:[10:9] ;default: 2'd0 ; */ | ||

| + | /*description: the functional selection signal of the pad*/ | ||

| + | #define RTC_IO_X32P_FUN_SEL_S 9 | ||

</source> | </source> | ||

| 第355行: | 第667行: | ||

</source> | </source> | ||

| − | + | <br> | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

=== rtc_sleep_prep === | === rtc_sleep_prep === | ||

| 第507行: | 第760行: | ||

<br><br> | <br><br> | ||

| − | === | + | === Undocumented === |

==== rtc_pads_muxsel ==== | ==== rtc_pads_muxsel ==== | ||

| + | |||

| + | Set the pad route to the digital IO_MUX (0) or RTC block (1) | ||

<source lang=bash> | <source lang=bash> | ||

| 第606行: | 第861行: | ||

} rtc_gpio_num_t; | } rtc_gpio_num_t; | ||

| + | /* | ||

| + | * set == 0, route to digital IO_MUX | ||

| + | * set == 1, route to RTC block | ||

| + | */ | ||

void rtc_pads_muxsel(rtc_gpio_num_t rtc_gpio_num, uint8_t sel); | void rtc_pads_muxsel(rtc_gpio_num_t rtc_gpio_num, uint8_t sel); | ||

</source> | </source> | ||

| 第612行: | 第871行: | ||

==== rtc_pads_funsel ==== | ==== rtc_pads_funsel ==== | ||

| + | |||

| + | Select the RTC function for this pad. | ||

<source lang=bash> | <source lang=bash> | ||

| 第661行: | 第922行: | ||

0x4008d485 <rtc_pads_funsel+133>: bbci a2, 4, 0x4008d4a5 <rtc_pads_funsel+165> | 0x4008d485 <rtc_pads_funsel+133>: bbci a2, 4, 0x4008d4a5 <rtc_pads_funsel+165> | ||

0x4008d488 <rtc_pads_funsel+136>: l32r a8, 0x4008c9c8 | 0x4008d488 <rtc_pads_funsel+136>: l32r a8, 0x4008c9c8 | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

...... | ...... | ||

...... | ...... | ||

| + | </source> | ||

| + | |||

| + | |||

| + | <source lang=cpp> | ||

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * sel == 0, select the function 0 of rtc | ||

| + | * sel == 1, select the function 1 of rtc | ||

| + | * sel == 2, select the function 2 of rtc | ||

| + | * sel == 3, select the function 3 of rtc | ||

| + | */ | ||

| + | void rtc_pads_funsel(rtc_gpio_num_t rtc_gpio_num, uint8_t sel); | ||

</source> | </source> | ||

| 第702行: | 第949行: | ||

==== rtc_pads_slpsel ==== | ==== rtc_pads_slpsel ==== | ||

| − | + | Sleep mode selection signal of the pad, Set to 1 to put the pad in sleep mode | |

| − | = | + | <source lang=bash> |

| + | 0x4008d648 <rtc_pads_slpsel>: entry a1, 32 | ||

| + | 0x4008d64b <rtc_pads_slpsel+3>: bbci a2, 0, 0x4008d66c <rtc_pads_slpsel+36> | ||

| + | 0x4008d64e <rtc_pads_slpsel+6>: l32r a8, 0x4008c9b4 | ||

| + | 0x4008d651 <rtc_pads_slpsel+9>: l32r a9, 0x4008add4 | ||

| + | 0x4008d654 <rtc_pads_slpsel+12>: memw | ||

| + | 0x4008d657 <rtc_pads_slpsel+15>: l32i a11, a8, 0 | ||

| + | 0x4008d65a <rtc_pads_slpsel+18>: extui a10, a3, 0, 1 | ||

| + | 0x4008d65d <rtc_pads_slpsel+21>: slli a10, a10, 21 | ||

| + | 0x4008d660 <rtc_pads_slpsel+24>: and a9, a11, a9 | ||

| + | 0x4008d663 <rtc_pads_slpsel+27>: or a9, a10, a9 | ||

| + | 0x4008d666 <rtc_pads_slpsel+30>: memw | ||

| + | 0x4008d669 <rtc_pads_slpsel+33>: s32i a9, a8, 0 | ||

| + | 0x4008d66c <rtc_pads_slpsel+36>: bbci a2, 1, 0x4008d68d <rtc_pads_slpsel+69> | ||

| + | 0x4008d66f <rtc_pads_slpsel+39>: l32r a8, 0x4008c9b4 | ||

| + | 0x4008d672 <rtc_pads_slpsel+42>: l32r a9, 0x4008bf98 | ||

| + | 0x4008d675 <rtc_pads_slpsel+45>: memw | ||

| + | 0x4008d678 <rtc_pads_slpsel+48>: l32i a11, a8, 0 | ||

| + | 0x4008d67b <rtc_pads_slpsel+51>: extui a10, a3, 0, 1 | ||

| + | 0x4008d67e <rtc_pads_slpsel+54>: slli a10, a10, 16 | ||

| + | 0x4008d681 <rtc_pads_slpsel+57>: and a9, a11, a9 | ||

| + | 0x4008d684 <rtc_pads_slpsel+60>: or a9, a10, a9 | ||

| + | 0x4008d687 <rtc_pads_slpsel+63>: memw | ||

| + | 0x4008d68a <rtc_pads_slpsel+66>: s32i a9, a8, 0 | ||

| + | 0x4008d68d <rtc_pads_slpsel+69>: bbci a2, 2, 0x4008d6ad <rtc_pads_slpsel+101> | ||

| + | 0x4008d690 <rtc_pads_slpsel+72>: l32r a8, 0x4008c9b4 | ||

| + | 0x4008d693 <rtc_pads_slpsel+75>: l32r a9, 0x400888dc | ||

| + | 0x4008d696 <rtc_pads_slpsel+78>: memw | ||

| + | 0x4008d699 <rtc_pads_slpsel+81>: l32i.n a11, a8, 0 | ||

| + | 0x4008d69b <rtc_pads_slpsel+83>: extui a10, a3, 0, 1 | ||

| + | 0x4008d69e <rtc_pads_slpsel+86>: slli a10, a10, 11 | ||

| + | 0x4008d6a1 <rtc_pads_slpsel+89>: and a9, a11, a9 | ||

| + | 0x4008d6a4 <rtc_pads_slpsel+92>: or a9, a10, a9 | ||

| + | 0x4008d6a7 <rtc_pads_slpsel+95>: memw | ||

| + | 0x4008d6aa <rtc_pads_slpsel+98>: s32i a9, a8, 0 | ||

| + | 0x4008d6ad <rtc_pads_slpsel+101>: bbci a2, 3, 0x4008d6cd <rtc_pads_slpsel+133> | ||

| + | 0x4008d6b0 <rtc_pads_slpsel+104>: l32r a8, 0x4008c9b4 | ||

| + | ...... | ||

| + | ...... | ||

| + | </source> | ||

| − | |||

| − | ==== | + | <source lang=cpp> |

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * sel == 1, put the pad in sleep mode | ||

| + | */ | ||

| + | void rtc_pads_slpsel(rtc_gpio_num_t rtc_gpio_num, uint8_t sel); | ||

| + | </source> | ||

<br> | <br> | ||

==== rtc_pads_slpie ==== | ==== rtc_pads_slpie ==== | ||

| + | |||

| + | <source lang=bash> | ||

| + | 0x4008da1c <rtc_pads_slpie>: entry a1, 32 | ||

| + | 0x4008da1f <rtc_pads_slpie+3>: bbci a2, 6, 0x4008da40 <rtc_pads_slpie+36> | ||

| + | 0x4008da22 <rtc_pads_slpie+6>: l32r a8, 0x4008bfa4 | ||

| + | 0x4008da25 <rtc_pads_slpie+9>: l32r a9, 0x4008da18 | ||

| + | 0x4008da28 <rtc_pads_slpie+12>: memw | ||

| + | 0x4008da2b <rtc_pads_slpie+15>: l32i a11, a8, 0 | ||

| + | 0x4008da2e <rtc_pads_slpie+18>: extui a10, a3, 0, 1 | ||

| + | 0x4008da31 <rtc_pads_slpie+21>: slli a10, a10, 13 | ||

| + | 0x4008da34 <rtc_pads_slpie+24>: and a9, a11, a9 | ||

| + | 0x4008da37 <rtc_pads_slpie+27>: or a9, a10, a9 | ||

| + | 0x4008da3a <rtc_pads_slpie+30>: memw | ||

| + | 0x4008da3d <rtc_pads_slpie+33>: s32i a9, a8, 0 | ||

| + | 0x4008da40 <rtc_pads_slpie+36>: bbci a2, 7, 0x4008da61 <rtc_pads_slpie+69> | ||

| + | 0x4008da43 <rtc_pads_slpie+39>: l32r a8, 0x4008bfb0 | ||

| + | 0x4008da46 <rtc_pads_slpie+42>: l32r a9, 0x4008da18 | ||

| + | 0x4008da49 <rtc_pads_slpie+45>: memw | ||

| + | 0x4008da4c <rtc_pads_slpie+48>: l32i a11, a8, 0 | ||

| + | 0x4008da4f <rtc_pads_slpie+51>: extui a10, a3, 0, 1 | ||

| + | 0x4008da52 <rtc_pads_slpie+54>: slli a10, a10, 13 | ||

| + | 0x4008da55 <rtc_pads_slpie+57>: and a9, a11, a9 | ||

| + | 0x4008da58 <rtc_pads_slpie+60>: or a9, a10, a9 | ||

| + | 0x4008da5b <rtc_pads_slpie+63>: memw | ||

| + | 0x4008da5e <rtc_pads_slpie+66>: s32i a9, a8, 0 | ||

| + | 0x4008da61 <rtc_pads_slpie+69>: bbci a2, 8, 0x4008da81 <rtc_pads_slpie+101> | ||

| + | 0x4008da64 <rtc_pads_slpie+72>: l32r a8, 0x4008c9bc | ||

| + | 0x4008da67 <rtc_pads_slpie+75>: l32r a9, 0x4008da18 | ||

| + | 0x4008da6a <rtc_pads_slpie+78>: memw | ||

| + | 0x4008da6d <rtc_pads_slpie+81>: l32i.n a11, a8, 0 | ||

| + | 0x4008da6f <rtc_pads_slpie+83>: extui a10, a3, 0, 1 | ||

| + | 0x4008da72 <rtc_pads_slpie+86>: slli a10, a10, 13 | ||

| + | 0x4008da75 <rtc_pads_slpie+89>: and a9, a11, a9 | ||

| + | 0x4008da78 <rtc_pads_slpie+92>: or a9, a10, a9 | ||

| + | 0x4008da7b <rtc_pads_slpie+95>: memw | ||

| + | 0x4008da7e <rtc_pads_slpie+98>: s32i a9, a8, 0 | ||

| + | 0x4008da81 <rtc_pads_slpie+101>: bbci a2, 9, 0x4008daa1 <rtc_pads_slpie+133> | ||

| + | 0x4008da84 <rtc_pads_slpie+104>: l32r a8, 0x4008c9bc | ||

| + | ...... | ||

| + | ...... | ||

| + | </source> | ||

| + | |||

| + | <source lang=cpp> | ||

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * sel == 1, put the pad in sleep mode | ||

| + | * | ||

| + | * Only valide for RTC_GPIO6 - RTC_GPIO17 | ||

| + | */ | ||

| + | void rtc_pads_slpie(rtc_gpio_num_t rtc_gpio_num, uint8_t enable); | ||

| + | </source> | ||

<br> | <br> | ||

==== rtc_pads_funie ==== | ==== rtc_pads_funie ==== | ||

| + | |||

| + | Input enable of the pad. | ||

| + | |||

| + | <source lang=bash> | ||

| + | 0x4008dba4 <rtc_pads_funie>: entry a1, 32 | ||

| + | 0x4008dba7 <rtc_pads_funie+3>: bbci a2, 6, 0x4008dbc8 <rtc_pads_funie+36> | ||

| + | 0x4008dbaa <rtc_pads_funie+6>: l32r a8, 0x4008bfa4 | ||

| + | 0x4008dbad <rtc_pads_funie+9>: l32r a9, 0x400888dc | ||

| + | 0x4008dbb0 <rtc_pads_funie+12>: memw | ||

| + | 0x4008dbb3 <rtc_pads_funie+15>: l32i a11, a8, 0 | ||

| + | 0x4008dbb6 <rtc_pads_funie+18>: extui a10, a3, 0, 1 | ||

| + | 0x4008dbb9 <rtc_pads_funie+21>: slli a10, a10, 11 | ||

| + | 0x4008dbbc <rtc_pads_funie+24>: and a9, a11, a9 | ||

| + | 0x4008dbbf <rtc_pads_funie+27>: or a9, a10, a9 | ||

| + | 0x4008dbc2 <rtc_pads_funie+30>: memw | ||

| + | 0x4008dbc5 <rtc_pads_funie+33>: s32i a9, a8, 0 | ||

| + | 0x4008dbc8 <rtc_pads_funie+36>: bbci a2, 7, 0x4008dbe9 <rtc_pads_funie+69> | ||

| + | 0x4008dbcb <rtc_pads_funie+39>: l32r a8, 0x4008bfb0 | ||

| + | 0x4008dbce <rtc_pads_funie+42>: l32r a9, 0x400888dc | ||

| + | 0x4008dbd1 <rtc_pads_funie+45>: memw | ||

| + | 0x4008dbd4 <rtc_pads_funie+48>: l32i a11, a8, 0 | ||

| + | 0x4008dbd7 <rtc_pads_funie+51>: extui a10, a3, 0, 1 | ||

| + | 0x4008dbda <rtc_pads_funie+54>: slli a10, a10, 11 | ||

| + | 0x4008dbdd <rtc_pads_funie+57>: and a9, a11, a9 | ||

| + | 0x4008dbe0 <rtc_pads_funie+60>: or a9, a10, a9 | ||

| + | 0x4008dbe3 <rtc_pads_funie+63>: memw | ||

| + | 0x4008dbe6 <rtc_pads_funie+66>: s32i a9, a8, 0 | ||

| + | 0x4008dbe9 <rtc_pads_funie+69>: bbci a2, 8, 0x4008dc09 <rtc_pads_funie+101> | ||

| + | 0x4008dbec <rtc_pads_funie+72>: l32r a8, 0x4008c9bc | ||

| + | ...... | ||

| + | ...... | ||

| + | </source> | ||

| + | |||

| + | <source lang=cpp> | ||

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * enable == 1, input enable | ||

| + | * enable == 0, input disable | ||

| + | * | ||

| + | * Only the RTC_GPIO6 - RTC_GPIO17 are valide | ||

| + | */ | ||

| + | void rtc_pads_funie (rtc_gpio_num_t rtc_gpio_num, uint8_t enable); | ||

| + | </source> | ||

| + | |||

| + | <br> | ||

| + | |||

| + | ==== rtc_pads_slpoe ==== | ||

| + | |||

| + | Output enable of the pad. | ||

| + | |||

| + | <source lang=bash> | ||

| + | 0x4008d890 <rtc_pads_slpoe>: entry a1, 32 | ||

| + | 0x4008d893 <rtc_pads_slpoe+3>: bbci a2, 6, 0x4008d8b4 <rtc_pads_slpoe+36> | ||

| + | 0x4008d896 <rtc_pads_slpoe+6>: l32r a8, 0x4008bfa4 | ||

| + | 0x4008d899 <rtc_pads_slpoe+9>: l32r a9, 0x40087114 | ||

| + | 0x4008d89c <rtc_pads_slpoe+12>: memw | ||

| + | 0x4008d89f <rtc_pads_slpoe+15>: l32i a11, a8, 0 | ||

| + | 0x4008d8a2 <rtc_pads_slpoe+18>: extui a10, a3, 0, 1 | ||

| + | 0x4008d8a5 <rtc_pads_slpoe+21>: slli a10, a10, 12 | ||

| + | 0x4008d8a8 <rtc_pads_slpoe+24>: and a9, a11, a9 | ||

| + | 0x4008d8ab <rtc_pads_slpoe+27>: or a9, a10, a9 | ||

| + | 0x4008d8ae <rtc_pads_slpoe+30>: memw | ||

| + | 0x4008d8b1 <rtc_pads_slpoe+33>: s32i a9, a8, 0 | ||

| + | 0x4008d8b4 <rtc_pads_slpoe+36>: bbci a2, 7, 0x4008d8d5 <rtc_pads_slpoe+69> | ||

| + | 0x4008d8b7 <rtc_pads_slpoe+39>: l32r a8, 0x4008bfb0 | ||

| + | 0x4008d8ba <rtc_pads_slpoe+42>: l32r a9, 0x40087114 | ||

| + | 0x4008d8bd <rtc_pads_slpoe+45>: memw | ||

| + | 0x4008d8c0 <rtc_pads_slpoe+48>: l32i a11, a8, 0 | ||

| + | 0x4008d8c3 <rtc_pads_slpoe+51>: extui a10, a3, 0, 1 | ||

| + | 0x4008d8c6 <rtc_pads_slpoe+54>: slli a10, a10, 12 | ||

| + | 0x4008d8c9 <rtc_pads_slpoe+57>: and a9, a11, a9 | ||

| + | 0x4008d8cc <rtc_pads_slpoe+60>: or a9, a10, a9 | ||

| + | 0x4008d8cf <rtc_pads_slpoe+63>: memw | ||

| + | 0x4008d8d2 <rtc_pads_slpoe+66>: s32i a9, a8, 0 | ||

| + | 0x4008d8d5 <rtc_pads_slpoe+69>: bbci a2, 8, 0x4008d8f5 <rtc_pads_slpoe+101> | ||

| + | 0x4008d8d8 <rtc_pads_slpoe+72>: l32r a8, 0x4008c9bc | ||

| + | ...... | ||

| + | ...... | ||

| + | </source> | ||

| + | |||

| + | <source lang=cpp> | ||

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * enable == 1, Output enable | ||

| + | * enable == 0, Output disable | ||

| + | * Only RTC_GPIO6 - RTC_GPIO17 are valide | ||

| + | */ | ||

| + | void rtc_pads_slpoe(rtc_gpio_num_t rtc_gpio_num, uint8_t enable); | ||

| + | </source> | ||

| + | |||

| + | <br> | ||

| + | |||

| + | ==== rtc_pads_hold ==== | ||

| + | |||

| + | <source lang=bash> | ||

| + | 0x4008e03c <rtc_pads_hold>: entry a1, 32 | ||

| + | 0x4008e03f <rtc_pads_hold+3>: bbci a2, 6, 0x4008e060 <rtc_pads_hold+36> | ||

| + | 0x4008e042 <rtc_pads_hold+6>: l32r a8, 0x4008bfa4 | ||

| + | 0x4008e045 <rtc_pads_hold+9>: l32r a9, 0x4008620c | ||

| + | 0x4008e048 <rtc_pads_hold+12>: memw | ||

| + | 0x4008e04b <rtc_pads_hold+15>: l32i a11, a8, 0 | ||

| + | 0x4008e04e <rtc_pads_hold+18>: extui a10, a3, 0, 1 | ||

| + | 0x4008e051 <rtc_pads_hold+21>: slli a10, a10, 29 | ||

| + | 0x4008e054 <rtc_pads_hold+24>: and a9, a11, a9 | ||

| + | 0x4008e057 <rtc_pads_hold+27>: or a9, a10, a9 | ||

| + | 0x4008e05a <rtc_pads_hold+30>: memw | ||

| + | 0x4008e05d <rtc_pads_hold+33>: s32i a9, a8, 0 | ||

| + | 0x4008e060 <rtc_pads_hold+36>: bbci a2, 7, 0x4008e081 <rtc_pads_hold+69> | ||

| + | 0x4008e063 <rtc_pads_hold+39>: l32r a8, 0x4008bfb0 | ||

| + | 0x4008e066 <rtc_pads_hold+42>: l32r a9, 0x4008620c | ||

| + | 0x4008e069 <rtc_pads_hold+45>: memw | ||

| + | 0x4008e06c <rtc_pads_hold+48>: l32i a11, a8, 0 | ||

| + | 0x4008e06f <rtc_pads_hold+51>: extui a10, a3, 0, 1 | ||

| + | 0x4008e072 <rtc_pads_hold+54>: slli a10, a10, 29 | ||

| + | 0x4008e075 <rtc_pads_hold+57>: and a9, a11, a9 | ||

| + | 0x4008e078 <rtc_pads_hold+60>: or a9, a10, a9 | ||

| + | 0x4008e07b <rtc_pads_hold+63>: memw | ||

| + | 0x4008e07e <rtc_pads_hold+66>: s32i a9, a8, 0 | ||

| + | 0x4008e081 <rtc_pads_hold+69>: bbci a2, 8, 0x4008e0a1 <rtc_pads_hold+101> | ||

| + | 0x4008e084 <rtc_pads_hold+72>: l32r a8, 0x4008c9bc | ||

| + | 0x4008e087 <rtc_pads_hold+75>: l32r a9, 0x4008620c | ||

| + | ...... | ||

| + | ...... | ||

| + | </source> | ||

| + | |||

| + | <source lang=cpp> | ||

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * hold == 1, Hold output value | ||

| + | * hold == 0, normal operation | ||

| + | * Only RTC_GPIO6 - RTC_GPIO17 are valide | ||

| + | */ | ||

| + | void rtc_pads_hold(rtc_gpio_num_t rtc_gpio_num, uint8_t hold); | ||

| + | </source> | ||

<br> | <br> | ||

==== rtc_pads_pu ==== | ==== rtc_pads_pu ==== | ||

| + | |||

| + | <source lang=bash> | ||

| + | 0x4008dd2c <rtc_pads_pu>: entry a1, 32 | ||

| + | 0x4008dd2f <rtc_pads_pu+3>: bbci a2, 6, 0x4008dd50 <rtc_pads_pu+36> | ||

| + | 0x4008dd32 <rtc_pads_pu+6>: l32r a8, 0x4008bfa4 | ||

| + | 0x4008dd35 <rtc_pads_pu+9>: l32r a9, 0x40084bc0 | ||

| + | 0x4008dd38 <rtc_pads_pu+12>: memw | ||

| + | 0x4008dd3b <rtc_pads_pu+15>: l32i a11, a8, 0 | ||

| + | 0x4008dd3e <rtc_pads_pu+18>: extui a10, a3, 0, 1 | ||

| + | 0x4008dd41 <rtc_pads_pu+21>: slli a10, a10, 27 | ||

| + | 0x4008dd44 <rtc_pads_pu+24>: and a9, a11, a9 | ||

| + | 0x4008dd47 <rtc_pads_pu+27>: or a9, a10, a9 | ||

| + | 0x4008dd4a <rtc_pads_pu+30>: memw | ||

| + | 0x4008dd4d <rtc_pads_pu+33>: s32i a9, a8, 0 | ||

| + | 0x4008dd50 <rtc_pads_pu+36>: bbci a2, 7, 0x4008dd71 <rtc_pads_pu+69> | ||

| + | 0x4008dd53 <rtc_pads_pu+39>: l32r a8, 0x4008bfb0 | ||

| + | 0x4008dd56 <rtc_pads_pu+42>: l32r a9, 0x40084bc0 | ||

| + | 0x4008dd59 <rtc_pads_pu+45>: memw | ||

| + | 0x4008dd5c <rtc_pads_pu+48>: l32i a11, a8, 0 | ||

| + | 0x4008dd5f <rtc_pads_pu+51>: extui a10, a3, 0, 1 | ||

| + | 0x4008dd62 <rtc_pads_pu+54>: slli a10, a10, 27 | ||

| + | 0x4008dd65 <rtc_pads_pu+57>: and a9, a11, a9 | ||

| + | 0x4008dd68 <rtc_pads_pu+60>: or a9, a10, a9 | ||

| + | 0x4008dd6b <rtc_pads_pu+63>: memw | ||

| + | 0x4008dd6e <rtc_pads_pu+66>: s32i a9, a8, 0 | ||

| + | 0x4008dd71 <rtc_pads_pu+69>: bbci a2, 8, 0x4008dd91 <rtc_pads_pu+101> | ||

| + | 0x4008dd74 <rtc_pads_pu+72>: l32r a8, 0x4008c9bc | ||

| + | 0x4008dd77 <rtc_pads_pu+75>: l32r a9, 0x40084bc0 | ||

| + | ...... | ||

| + | ...... | ||

| + | </source> | ||

| + | |||

| + | <source lang=cpp> | ||

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * pu == 1, pull-up enable | ||

| + | * pu == 0, pull-up disable | ||

| + | * Only RTC_GPIO6 - RTC_GPIO17 are valide | ||

| + | */ | ||

| + | void rtc_pads_pu(rtc_gpio_num_t rtc_gpio_num, uint8_t pu); | ||

| + | </source> | ||

<br> | <br> | ||

==== rtc_pads_pd ==== | ==== rtc_pads_pd ==== | ||

| + | |||

| + | <source lang=bash> | ||

| + | 0x4008deb4 <rtc_pads_pd>: entry a1, 32 | ||

| + | 0x4008deb7 <rtc_pads_pd+3>: bbci a2, 6, 0x4008ded8 <rtc_pads_pd+36> | ||

| + | 0x4008deba <rtc_pads_pd+6>: l32r a8, 0x4008bfa4 | ||

| + | 0x4008debd <rtc_pads_pd+9>: l32r a9, 0x40087110 | ||

| + | 0x4008dec0 <rtc_pads_pd+12>: memw | ||

| + | 0x4008dec3 <rtc_pads_pd+15>: l32i a11, a8, 0 | ||

| + | 0x4008dec6 <rtc_pads_pd+18>: extui a10, a3, 0, 1 | ||

| + | 0x4008dec9 <rtc_pads_pd+21>: slli a10, a10, 28 | ||

| + | 0x4008decc <rtc_pads_pd+24>: and a9, a11, a9 | ||

| + | 0x4008decf <rtc_pads_pd+27>: or a9, a10, a9 | ||

| + | 0x4008ded2 <rtc_pads_pd+30>: memw | ||

| + | 0x4008ded5 <rtc_pads_pd+33>: s32i a9, a8, 0 | ||

| + | 0x4008ded8 <rtc_pads_pd+36>: bbci a2, 7, 0x4008def9 <rtc_pads_pd+69> | ||

| + | 0x4008dedb <rtc_pads_pd+39>: l32r a8, 0x4008bfb0 | ||

| + | 0x4008dede <rtc_pads_pd+42>: l32r a9, 0x40087110 | ||

| + | 0x4008dee1 <rtc_pads_pd+45>: memw | ||

| + | 0x4008dee4 <rtc_pads_pd+48>: l32i a11, a8, 0 | ||

| + | 0x4008dee7 <rtc_pads_pd+51>: extui a10, a3, 0, 1 | ||

| + | 0x4008deea <rtc_pads_pd+54>: slli a10, a10, 28 | ||

| + | 0x4008deed <rtc_pads_pd+57>: and a9, a11, a9 | ||

| + | 0x4008def0 <rtc_pads_pd+60>: or a9, a10, a9 | ||

| + | 0x4008def3 <rtc_pads_pd+63>: memw | ||

| + | 0x4008def6 <rtc_pads_pd+66>: s32i a9, a8, 0 | ||

| + | 0x4008def9 <rtc_pads_pd+69>: bbci a2, 8, 0x4008df19 <rtc_pads_pd+101> | ||

| + | 0x4008defc <rtc_pads_pd+72>: l32r a8, 0x4008c9bc | ||

| + | 0x4008deff <rtc_pads_pd+75>: l32r a9, 0x40087110 | ||

| + | ...... | ||

| + | ...... | ||

| + | </source> | ||

| + | |||

| + | <source lang=cpp> | ||

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * pd == 1, pull-down enable | ||

| + | * pd == 0, pull-down disable | ||

| + | * Only RTC_GPIO6 - RTC_GPIO17 are valide | ||

| + | */ | ||

| + | void rtc_pads_pd(rtc_gpio_num_t rtc_gpio_num, uint8_t pd); | ||

| + | </source> | ||

<br> | <br> | ||

| 第787行: | 第1,394行: | ||

==== rtc_pad_ext_wakeup ==== | ==== rtc_pad_ext_wakeup ==== | ||

| − | + | Following: | |

| − | ==== | + | * p1 is the 1st parameter of rtc_pad_ext_wakeup |

| + | * p2 is the 2nd parameter of rtc_pad_ext_wakeup | ||

| + | * p3 is the 3rd parameter of rtc_pad_ext_wakeup | ||

| + | |||

| + | <source lang=c> | ||

| + | 0x4008ee9c <rtc_pad_ext_wakeup>: entry a1, 32 | ||

| + | 0x4008ee9f <rtc_pad_ext_wakeup+3>: mov.n a10, a2 | ||

| + | 0x4008eea1 <rtc_pad_ext_wakeup+5>: movi.n a11, 1 | ||

| + | 0x4008eea3 <rtc_pad_ext_wakeup+7>: call8 0x4008d2f4 <rtc_pads_muxsel> /* rtc_pads_muxsel (p1, 1) */ | ||

| + | |||

| + | 0x4008eea6 <rtc_pad_ext_wakeup+10>: mov.n a10, a2 | ||

| + | 0x4008eea8 <rtc_pad_ext_wakeup+12>: movi.n a11, 0 | ||

| + | 0x4008eeaa <rtc_pad_ext_wakeup+14>: call8 0x4008d54c <rtc_pads_funsel> /* rtc_pads_funsel (p1, 0) */ | ||

| + | |||

| + | 0x4008eead <rtc_pad_ext_wakeup+17>: l32r a8, 0x4008edf4 /* a8 = *(4008edf4) = 0x3ff4840c, RTC_GPIO_ENABLE_REG */ | ||

| + | 0x4008eeb0 <rtc_pad_ext_wakeup+20>: slli a9, a2, 14 | ||

| + | 0x4008eeb3 <rtc_pad_ext_wakeup+23>: memw | ||

| + | 0x4008eeb6 <rtc_pad_ext_wakeup+26>: l32i.n a10, a8, 0 /* a10 = read RTC_GPIO_ENABLE_REG */ | ||

| + | 0x4008eeb8 <rtc_pad_ext_wakeup+28>: movi.n a11, -1 /* a11 = 0xffff ffff */ | ||

| + | 0x4008eeba <rtc_pad_ext_wakeup+30>: xor a9, a11, a9 /* a9 = ~a9 */ | ||

| + | 0x4008eebd <rtc_pad_ext_wakeup+33>: and a9, a9, a10 /* a9 = a10 & a9 */ | ||

| + | 0x4008eec0 <rtc_pad_ext_wakeup+36>: memw | ||

| + | 0x4008eec3 <rtc_pad_ext_wakeup+39>: s32i.n a9, a8, 0 /* store to RTC_GPIO_ENABLE_REG, disable the output of the RTC_PAD */ | ||

| + | |||

| + | 0x4008eec5 <rtc_pad_ext_wakeup+41>: mov.n a10, a2 | ||

| + | 0x4008eec7 <rtc_pad_ext_wakeup+43>: movi a11, 1 | ||

| + | 0x4008eeca <rtc_pad_ext_wakeup+46>: call8 0x4008d794 <rtc_pads_slpsel> /* rtc_pads_slpsel (p1, 1) */ | ||

| + | |||

| + | 0x4008eecd <rtc_pad_ext_wakeup+49>: mov.n a10, a2 | ||

| + | 0x4008eecf <rtc_pad_ext_wakeup+51>: movi a11, 0 | ||

| + | 0x4008eed2 <rtc_pad_ext_wakeup+54>: call8 0x4008d9dc <rtc_pads_slpoe> /* rtc_pads_slpoe (p1, 0) */ | ||

| + | |||

| + | 0x4008eed5 <rtc_pad_ext_wakeup+57>: mov.n a10, a2 | ||

| + | 0x4008eed7 <rtc_pad_ext_wakeup+59>: movi a11, 1 | ||

| + | 0x4008eeda <rtc_pad_ext_wakeup+62>: call8 0x4008db68 <rtc_pads_slpie> /* rtc_pads_slpie (p1, 1) */ | ||

| + | |||

| + | 0x4008eedd <rtc_pad_ext_wakeup+65>: mov.n a10, a2 | ||

| + | 0x4008eedf <rtc_pad_ext_wakeup+67>: movi a11, 1 | ||

| + | 0x4008eee2 <rtc_pad_ext_wakeup+70>: call8 0x4008dcf0 <rtc_pads_funie> /* rtc_pads_funie (p1, 1) */ | ||

| + | |||

| + | 0x4008eee5 <rtc_pad_ext_wakeup+73>: mov.n a10, a2 | ||

| + | 0x4008eee7 <rtc_pad_ext_wakeup+75>: movi a11, 0 | ||

| + | 0x4008eeea <rtc_pad_ext_wakeup+78>: call8 0x4008de78 <rtc_pads_pu> /* rtc_pads_pu (p1, 0) */ | ||

| + | |||

| + | 0x4008eeed <rtc_pad_ext_wakeup+81>: mov.n a10, a2 | ||

| + | 0x4008eeef <rtc_pad_ext_wakeup+83>: movi.n a11, 0 | ||

| + | 0x4008eef1 <rtc_pad_ext_wakeup+85>: call8 0x4008e000 <rtc_pads_pd> /* rtc_pads_pd (p1, 0) */ | ||

| + | |||

| + | 0x4008eef4 <rtc_pad_ext_wakeup+88>: l32r a8, 0x4008ee90 /* a8 = *(0x4008ee90) = 0x3ff484bc, RTC_IO_EXT_WAKEUP0_REG */ | ||

| + | 0x4008eef7 <rtc_pad_ext_wakeup+91>: l32r a2, 0x4008ee94 /* a2 = *(0x4008ee94) = 0x07ffffff */ | ||

| + | 0x4008eefa <rtc_pad_ext_wakeup+94>: memw | ||

| + | 0x4008eefd <rtc_pad_ext_wakeup+97>: l32i.n a9, a8, 0 /* a9 = read RTC_IO_EXT_WAKEUP0_REG */ | ||

| + | 0x4008eeff <rtc_pad_ext_wakeup+99>: slli a3, a3, 27 /* a3 = p2 << 27 */ | ||

| + | 0x4008ef02 <rtc_pad_ext_wakeup+102>: and a9, a9, a2 /* a9 = RTC_IO_EXT_WAKEUP0_REG & 0x07ff ffff */ | ||

| + | 0x4008ef05 <rtc_pad_ext_wakeup+105>: or a3, a3, a9 /* a3 = (p2 << 27) | a9 */ | ||

| + | |||

| + | 0x4008ef08 <rtc_pad_ext_wakeup+108>: l32r a2, 0x4008ee98 /* a2 = *(0x4008ee98) = 0x3ff48060, RTC_CNTL_EXT_WAKEUP_CONF_REG */ | ||

| + | 0x4008ef0b <rtc_pad_ext_wakeup+111>: memw | ||

| + | 0x4008ef0e <rtc_pad_ext_wakeup+114>: s32i.n a3, a8, 0 /* write to RTC_IO_EXT_WAKEUP0_REG */ | ||

| + | |||

| + | 0x4008ef10 <rtc_pad_ext_wakeup+116>: memw | ||

| + | 0x4008ef13 <rtc_pad_ext_wakeup+119>: l32i.n a8, a2, 0 /* a8 = read RTC_CNTL_EXT_WAKEUP_CONF_REG */ | ||

| + | 0x4008ef15 <rtc_pad_ext_wakeup+121>: l32r a3, 0x4008838c /* a3 = *(0x4008838c) = 0xbfffffff */ | ||

| + | |||

| + | 0x4008ef18 <rtc_pad_ext_wakeup+124>: extui a4, a4, 0, 1 /* a4 = p3[0] */ | ||

| + | 0x4008ef1b <rtc_pad_ext_wakeup+127>: slli a4, a4, 30 /* a4 = a4 << 30 */ | ||

| + | |||

| + | 0x4008ef1e <rtc_pad_ext_wakeup+130>: and a3, a8, a3 /* a3 = a8 & a3 = RTC_CNTL_EXT_WAKEUP_CONF_REG & 0xbfff ffff */ | ||

| + | 0x4008ef21 <rtc_pad_ext_wakeup+133>: or a4, a4, a3 /* a4 = RTC_CNTL_EXT_WAKEUP_CONF_REG & 0xbfff ffff | (p3[0] << 30) */ | ||

| + | 0x4008ef24 <rtc_pad_ext_wakeup+136>: memw | ||

| + | 0x4008ef27 <rtc_pad_ext_wakeup+139>: s32i.n a4, a2, 0 /* write to RTC_CNTL_EXT_WAKEUP_CONF_REG */ | ||

| + | |||

| + | /* use the EXT_WAKEUP0, 0: external wakeup at low level 1: external wakeup at high level */ | ||

| + | |||

| + | 0x4008ef29 <rtc_pad_ext_wakeup+141>: retw.n | ||

| + | </source> | ||

| + | |||

| + | So: | ||

| + | |||

| + | <source lang=c> | ||

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * rtc_io_num is the number of rtc_pad. e.g. The number of RTC_GPIO5 is 5 | ||

| + | * wakeup_level = 0: external wakeup at low level | ||

| + | * wakeup_level = 1: external wakeup at high level | ||

| + | */ | ||

| + | void rtc_pad_ext_wakeup(rtc_gpio_num_t rtc_pad, uint8_t rtc_io_num, uint8_t wakeup_level); | ||

| + | </source> | ||

<br> | <br> | ||

==== rtc_cmd_ext_wakeup ==== | ==== rtc_cmd_ext_wakeup ==== | ||

| + | |||

| + | <source lang=bash> | ||

| + | 0x4008ef2c <rtc_cmd_ext_wakeup>: entry a1, 32 | ||

| + | 0x4008ef2f <rtc_cmd_ext_wakeup+3>: mov.n a10, a2 | ||

| + | 0x4008ef31 <rtc_cmd_ext_wakeup+5>: movi.n a11, 1 | ||

| + | 0x4008ef33 <rtc_cmd_ext_wakeup+7>: call8 0x4008d2f4 <rtc_pads_muxsel> | ||

| + | 0x4008ef36 <rtc_cmd_ext_wakeup+10>: mov.n a10, a2 | ||

| + | 0x4008ef38 <rtc_cmd_ext_wakeup+12>: movi.n a11, 0 | ||

| + | 0x4008ef3a <rtc_cmd_ext_wakeup+14>: call8 0x4008d54c <rtc_pads_funsel> | ||

| + | 0x4008ef3d <rtc_cmd_ext_wakeup+17>: l32r a8, 0x4008edf4 | ||

| + | 0x4008ef40 <rtc_cmd_ext_wakeup+20>: slli a9, a2, 14 | ||

| + | 0x4008ef43 <rtc_cmd_ext_wakeup+23>: memw | ||

| + | 0x4008ef46 <rtc_cmd_ext_wakeup+26>: l32i.n a10, a8, 0 | ||

| + | 0x4008ef48 <rtc_cmd_ext_wakeup+28>: movi.n a11, -1 | ||

| + | 0x4008ef4a <rtc_cmd_ext_wakeup+30>: xor a9, a11, a9 | ||

| + | 0x4008ef4d <rtc_cmd_ext_wakeup+33>: and a9, a9, a10 | ||

| + | 0x4008ef50 <rtc_cmd_ext_wakeup+36>: memw | ||

| + | 0x4008ef53 <rtc_cmd_ext_wakeup+39>: s32i.n a9, a8, 0 | ||

| + | 0x4008ef55 <rtc_cmd_ext_wakeup+41>: mov.n a10, a2 | ||

| + | 0x4008ef57 <rtc_cmd_ext_wakeup+43>: movi a11, 1 | ||

| + | 0x4008ef5a <rtc_cmd_ext_wakeup+46>: call8 0x4008d794 <rtc_pads_slpsel> | ||

| + | 0x4008ef5d <rtc_cmd_ext_wakeup+49>: mov.n a10, a2 | ||

| + | 0x4008ef5f <rtc_cmd_ext_wakeup+51>: movi a11, 0 | ||

| + | 0x4008ef62 <rtc_cmd_ext_wakeup+54>: call8 0x4008d9dc <rtc_pads_slpoe> | ||

| + | 0x4008ef65 <rtc_cmd_ext_wakeup+57>: mov.n a10, a2 | ||

| + | 0x4008ef67 <rtc_cmd_ext_wakeup+59>: movi a11, 1 | ||

| + | 0x4008ef6a <rtc_cmd_ext_wakeup+62>: call8 0x4008db68 <rtc_pads_slpie> | ||

| + | 0x4008ef6d <rtc_cmd_ext_wakeup+65>: mov.n a10, a2 | ||

| + | 0x4008ef6f <rtc_cmd_ext_wakeup+67>: movi a11, 1 | ||

| + | 0x4008ef72 <rtc_cmd_ext_wakeup+70>: call8 0x4008dcf0 <rtc_pads_funie> | ||

| + | 0x4008ef75 <rtc_cmd_ext_wakeup+73>: mov.n a10, a2 | ||

| + | 0x4008ef77 <rtc_cmd_ext_wakeup+75>: movi a11, 0 | ||

| + | 0x4008ef7a <rtc_cmd_ext_wakeup+78>: call8 0x4008de78 <rtc_pads_pu> | ||

| + | 0x4008ef7d <rtc_cmd_ext_wakeup+81>: mov.n a10, a2 | ||

| + | 0x4008ef7f <rtc_cmd_ext_wakeup+83>: movi.n a11, 0 | ||

| + | 0x4008ef81 <rtc_cmd_ext_wakeup+85>: call8 0x4008e000 <rtc_pads_pd> | ||

| + | |||

| + | 0x4008ef84 <rtc_cmd_ext_wakeup+88>: l32r a8, 0x4008ee90 | ||

| + | 0x4008ef87 <rtc_cmd_ext_wakeup+91>: l32r a2, 0x4008ee94 | ||

| + | 0x4008ef8a <rtc_cmd_ext_wakeup+94>: memw | ||

| + | 0x4008ef8d <rtc_cmd_ext_wakeup+97>: l32i.n a9, a8, 0 | ||

| + | 0x4008ef8f <rtc_cmd_ext_wakeup+99>: slli a3, a3, 27 | ||

| + | 0x4008ef92 <rtc_cmd_ext_wakeup+102>: and a9, a9, a2 | ||

| + | 0x4008ef95 <rtc_cmd_ext_wakeup+105>: or a3, a3, a9 | ||

| + | 0x4008ef98 <rtc_cmd_ext_wakeup+108>: l32r a2, 0x4008ee98 /* a2 = *(0x4008ee98) = 0x3ff48060, RTC_CNTL_EXT_WAKEUP_CONF_REG */ | ||

| + | 0x4008ef9b <rtc_cmd_ext_wakeup+111>: memw | ||

| + | 0x4008ef9e <rtc_cmd_ext_wakeup+114>: s32i.n a3, a8, 0 | ||

| + | 0x4008efa0 <rtc_cmd_ext_wakeup+116>: memw | ||

| + | |||

| + | /* All above is same as rtc_pad_ext_wakeup ! */ | ||

| + | |||

| + | 0x4008efa3 <rtc_cmd_ext_wakeup+119>: l32i.n a8, a2, 0 /* a8 = read RTC_CNTL_EXT_WAKEUP_CONF_REG */ | ||

| + | 0x4008efa5 <rtc_cmd_ext_wakeup+121>: l32r a3, 0x400805fc /* a3 = *(0x400805fc) = 0x40000000 */ | ||

| + | 0x4008efa8 <rtc_cmd_ext_wakeup+124>: or a3, a8, a3 /* a3 = 0x40000000 | RTC_CNTL_EXT_WAKEUP_CONF_REG, Set BIT(30) to 1 */ | ||

| + | |||

| + | /* EXT_WAKEUP0, external wake up at high level */ | ||

| + | |||

| + | 0x4008efab <rtc_cmd_ext_wakeup+127>: memw | ||

| + | 0x4008efae <rtc_cmd_ext_wakeup+130>: s32i.n a3, a2, 0 | ||

| + | 0x4008efb0 <rtc_cmd_ext_wakeup+132>: retw.n | ||

| + | </source> | ||

| + | |||

| + | So: | ||

| + | |||

| + | <source lang=c> | ||

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * rtc_io_num is the number of rtc_pad. e.g. The number of RTC_GPIO5 is 5 | ||

| + | */ | ||

| + | void rtc_cmd_ext_wakeup(rtc_gpio_num_t rtc_pad, uint8_t rtc_io_num); | ||

| + | </source> | ||

| + | |||

| + | <br> | ||

| + | |||

| + | ==== rtc_pad_gpio_wakeup ==== | ||

| + | |||

| + | Only available in light sleep mode | ||

| + | |||

| + | <source lang=bash> | ||

| + | 0x4008edfc <rtc_pad_gpio_wakeup>: entry a1, 32 | ||

| + | 0x4008edff <rtc_pad_gpio_wakeup+3>: mov.n a10, a2 | ||

| + | 0x4008ee01 <rtc_pad_gpio_wakeup+5>: movi.n a11, 1 | ||

| + | 0x4008ee03 <rtc_pad_gpio_wakeup+7>: call8 0x4008d2f4 <rtc_pads_muxsel> /* rtc_pads_muxsel(p1, 1) */ | ||

| + | 0x4008ee06 <rtc_pad_gpio_wakeup+10>: mov.n a10, a2 | ||

| + | 0x4008ee08 <rtc_pad_gpio_wakeup+12>: movi.n a11, 0 | ||

| + | 0x4008ee0a <rtc_pad_gpio_wakeup+14>: call8 0x4008d54c <rtc_pads_funsel> /* rtc_pad_funsel(p1, 0) */ | ||

| + | |||

| + | 0x4008ee0d <rtc_pad_gpio_wakeup+17>: l32r a8, 0x4008edf4 /* a8 = 0x3ff4840c, RTC_GPIO_ENABLE_REG */ | ||

| + | 0x4008ee10 <rtc_pad_gpio_wakeup+20>: movi.n a9, -1 /* a9 = 0xffff ffff */ | ||

| + | 0x4008ee12 <rtc_pad_gpio_wakeup+22>: memw | ||

| + | 0x4008ee15 <rtc_pad_gpio_wakeup+25>: l32i.n a10, a8, 0 /* a10 = read RTC_GPIO_ENABLE_REG */ | ||

| + | 0x4008ee17 <rtc_pad_gpio_wakeup+27>: xor a9, a9, a2 /* a9 = ~p1 = p1 ^ 0xffff ffff */ | ||

| + | 0x4008ee1a <rtc_pad_gpio_wakeup+30>: and a9, a9, a10 /* a9 = a9 & RTC_GPIO_ENABLE_REG */ | ||

| + | 0x4008ee1d <rtc_pad_gpio_wakeup+33>: memw | ||

| + | 0x4008ee20 <rtc_pad_gpio_wakeup+36>: s32i.n a9, a8, 0 | ||

| + | |||

| + | 0x4008ee22 <rtc_pad_gpio_wakeup+38>: mov.n a10, a2 | ||

| + | 0x4008ee24 <rtc_pad_gpio_wakeup+40>: movi a11, 1 | ||

| + | 0x4008ee27 <rtc_pad_gpio_wakeup+43>: call8 0x4008d794 <rtc_pads_slpsel> /* rtc_pads_slpsel(p1, 1) */ | ||

| + | 0x4008ee2a <rtc_pad_gpio_wakeup+46>: mov.n a10, a2 | ||

| + | 0x4008ee2c <rtc_pad_gpio_wakeup+48>: movi a11, 0 | ||

| + | 0x4008ee2f <rtc_pad_gpio_wakeup+51>: call8 0x4008d9dc <rtc_pads_slpoe> /* rtc_pads_slpoe(p1, 0) */ | ||

| + | 0x4008ee32 <rtc_pad_gpio_wakeup+54>: mov.n a10, a2 | ||

| + | 0x4008ee34 <rtc_pad_gpio_wakeup+56>: movi a11, 1 | ||

| + | 0x4008ee37 <rtc_pad_gpio_wakeup+59>: call8 0x4008db68 <rtc_pads_slpie> /* rtc_pads_slpie(p1, 1) */ | ||

| + | 0x4008ee3a <rtc_pad_gpio_wakeup+62>: mov.n a10, a2 | ||

| + | 0x4008ee3c <rtc_pad_gpio_wakeup+64>: movi a11, 1 | ||

| + | 0x4008ee3f <rtc_pad_gpio_wakeup+67>: call8 0x4008dcf0 <rtc_pads_funie> /* rtc_pads_funie(p1, 1) */ | ||

| + | 0x4008ee42 <rtc_pad_gpio_wakeup+70>: mov.n a10, a2 | ||

| + | 0x4008ee44 <rtc_pad_gpio_wakeup+72>: movi.n a11, 0 | ||

| + | 0x4008ee46 <rtc_pad_gpio_wakeup+74>: call8 0x4008de78 <rtc_pads_pu> /* rtc_pads_pu(p1, 0) */ | ||

| + | 0x4008ee49 <rtc_pad_gpio_wakeup+77>: mov.n a10, a2 | ||

| + | 0x4008ee4b <rtc_pad_gpio_wakeup+79>: movi.n a11, 0 | ||

| + | 0x4008ee4d <rtc_pad_gpio_wakeup+81>: call8 0x4008e000 <rtc_pads_pd> /* rtc_pads_pd(p1, 0) */ | ||

| + | |||

| + | 0x4008ee50 <rtc_pad_gpio_wakeup+84>: extui a3, a3, 0, 3 /* a3 = p2[2:0] */ | ||

| + | 0x4008ee53 <rtc_pad_gpio_wakeup+87>: l32r a8, 0x4008edf0 /* a8 = *(0x4008edf0) = 0x3ff48428, RTC_GPIO_PIN0_REG */ | ||

| + | 0x4008ee56 <rtc_pad_gpio_wakeup+90>: l32r a10, 0x4008edf8 /* a10 = *(0x4008edf8) = 0x3ff48470 */ | ||

| + | |||

| + | /* RTC_GPIO_PIN17_REG addr is 0x3ff4846c */ | ||

| + | |||

| + | 0x4008ee59 <rtc_pad_gpio_wakeup+93>: slli a14, a3, 7 /* a14 = p2[2:0] << 7 */ | ||

| + | 0x4008ee5c <rtc_pad_gpio_wakeup+96>: movi.n a9, 1 | ||

| + | 0x4008ee5e <rtc_pad_gpio_wakeup+98>: movi a13, 0x400 | ||

| + | 0x4008ee61 <rtc_pad_gpio_wakeup+101>: movi a12, 0xfffffc7f | ||

| + | 0x4008ee64 <rtc_pad_gpio_wakeup+104>: bnone a9, a2, 0x4008ee84 <rtc_pad_gpio_wakeup+136> /* branch; if (a9 & a2 == 0); */ | ||

| + | 0x4008ee67 <rtc_pad_gpio_wakeup+107>: memw | ||

| + | 0x4008ee6a <rtc_pad_gpio_wakeup+110>: l32i.n a11, a8, 0 /* a11 = read RTC_GPIO_PINx_REG */ | ||

| + | 0x4008ee6c <rtc_pad_gpio_wakeup+112>: or a11, a11, a13 /* a11 = RTC_GPIO_PINx_REG | 0x400 */ | ||

| + | 0x4008ee6f <rtc_pad_gpio_wakeup+115>: memw | ||

| + | 0x4008ee72 <rtc_pad_gpio_wakeup+118>: s32i.n a11, a8, 0 /* write to RTC_GPIO_PINx_REG */ | ||

| + | |||

| + | 0x4008ee74 <rtc_pad_gpio_wakeup+120>: memw | ||

| + | 0x4008ee77 <rtc_pad_gpio_wakeup+123>: l32i.n a11, a8, 0 /* a11 = read RTC_GPIO_PINx_REG */ | ||

| + | 0x4008ee79 <rtc_pad_gpio_wakeup+125>: and a11, a11, a12 /* a11 = RTC_GPIO_PINx_REG & 0xfffffc7f */ | ||

| + | 0x4008ee7c <rtc_pad_gpio_wakeup+128>: or a11, a11, a14 /* a11 |= (p2[2:0] << 7) */ | ||

| + | 0x4008ee7f <rtc_pad_gpio_wakeup+131>: memw | ||

| + | 0x4008ee82 <rtc_pad_gpio_wakeup+134>: s32i.n a11, a8, 0 /* write to RTC_GPIO_PIN0_REG */ | ||

| + | |||

| + | 0x4008ee84 <rtc_pad_gpio_wakeup+136>: addi.n a8, a8, 4 /* a8 = 0x3ff48428 + i*4, RTC_GPIO_PINx_REG */ | ||

| + | 0x4008ee86 <rtc_pad_gpio_wakeup+138>: slli a9, a9, 1 /* a9 <<= 1 */ | ||

| + | 0x4008ee89 <rtc_pad_gpio_wakeup+141>: bne a8, a10, 0x4008ee64 <rtc_pad_gpio_wakeup+104> /* branch; if (a8 != a10); */ | ||

| + | 0x4008ee8c <rtc_pad_gpio_wakeup+144>: retw.n | ||

| + | </source> | ||

| + | |||

| + | So: | ||

| + | |||

| + | <source lang=c> | ||

| + | typedef enum { | ||

| + | RTC_GPIO0 = BIT(0), | ||

| + | RTC_GPIO1 = BIT(1), | ||

| + | ...... | ||

| + | ...... | ||

| + | RTC_GPIO17 = BIT(17) | ||

| + | } rtc_gpio_num_t; | ||

| + | |||

| + | /* | ||

| + | * int_type: | ||

| + | * 0: GPIO interrupt disable | ||

| + | * 1: rising edge | ||

| + | * 2: falling edge trigger | ||

| + | * 3: any edge trigger | ||

| + | * 4: low level trigger | ||

| + | * 5: high level trigger | ||

| + | */ | ||

| + | void rtc_pad_gpio_wakeup(rtc_gpio_num_t rtc_pad, uint8_t int_type); | ||

| + | </source> | ||

<br> | <br> | ||

| 第822行: | 第1,697行: | ||

=== External Wakeup === | === External Wakeup === | ||

| + | |||

| + | Please refer to: [[ESP32 RTC External Wakeup]] | ||

<source lang=cpp> | <source lang=cpp> | ||

| 第916行: | 第1,793行: | ||

<br><br> | <br><br> | ||

| − | == ULP | + | == ULP == |

| − | + | ULP coprocessor is a simple FSM which is designed to perform measurements using ADC, temperature sensor, and external I2C sensors, while main processors are in deep sleep mode. | |

| − | + | ULP coprocessor can access RTC_SLOW_MEM memory region, and registers in RTC_CNTL, RTC_IO, and SARADC peripherals. | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ULP coprocessor uses fixed-width 32-bit instructions, 32-bit memory addressing, and has 4 general purpose 16-bit registers. | |

| − | + | More details, please refer to [[ESP32 ULP]] | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | <br><br> | |

| − | + | == Demo == | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | === | + | === Smoke Detector === |

| − | + | More details, please refer to: [[ESP32 Smoke Detector]] | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | <br><br> | |

| − | + | ||

| − | < | + | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | === | + | === Touch Pad === |

| − | + | More details, please refer to: [[ESP32 Touch Pad]] | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

<br><br> | <br><br> | ||

| − | + | <br><br> | |

| − | + | <br><br> | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | < | + | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||