GD32

来自Jack's Lab

(版本间的差异)

(→Overview) |

(→GD32VF103T8U6) |

||

| (未显示1个用户的15个中间版本) | |||

| 第1行: | 第1行: | ||

== Overview == | == Overview == | ||

| − | http://gd32mcu.com/cn/product/m23 | + | * http://gd32mcu.com/cn/product/m23 |

| + | * http://gd32mcu.com/cn/product/risc | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == ARM == | ||

=== GD32E230G8U6 === | === GD32E230G8U6 === | ||

| 第11行: | 第16行: | ||

* GPIO x23 | * GPIO x23 | ||

* ADC x1 | * ADC x1 | ||

| − | * 1.8V ~ 3.6V, 5V | + | * 1.8V ~ 3.6V, 5V 容忍 I/O |

| − | * QFN28 | + | * QFN28, 4x4mm |

* [http://gd32mcu.com/data/documents/shujushouce/GD32E230xx_Datasheet_Rev1.4.pdf GD32E230xx datasheet] | * [http://gd32mcu.com/data/documents/shujushouce/GD32E230xx_Datasheet_Rev1.4.pdf GD32E230xx datasheet] | ||

| + | |||

| + | [[文件:GD32E230-QFN28.png]] | ||

<br> | <br> | ||

| 第20行: | 第27行: | ||

* 32 bit Cortex®-M23 Core, up to 72MHz | * 32 bit Cortex®-M23 Core, up to 72MHz | ||

| − | * 64KB Flash, 8KB RAM; | + | * 64KB Flash, 8KB RAM; K6U6 (32KB/6KB) |

* I2C x2; SPI x2; USART x2 | * I2C x2; SPI x2; USART x2 | ||

* RTC x1 | * RTC x1 | ||

| 第26行: | 第33行: | ||

* ADC x1 | * ADC x1 | ||

* 1.8V ~ 3.6V, 5V 容忍I/O | * 1.8V ~ 3.6V, 5V 容忍I/O | ||

| − | * QFN32 | + | * QFN32, 5x5mm |

* [http://gd32mcu.com/data/documents/shujushouce/GD32E230xx_Datasheet_Rev1.4.pdf GD32E230xx datasheet] | * [http://gd32mcu.com/data/documents/shujushouce/GD32E230xx_Datasheet_Rev1.4.pdf GD32E230xx datasheet] | ||

| + | |||

| + | [[文件:GD32E230-QFN32.png]] | ||

<br> | <br> | ||

| − | == | + | == RISC-V == |

| + | |||

| + | http://gd32mcu.com/cn/product/risc | ||

| + | |||

| + | === GD32VF103T8U6 === | ||

| + | |||

| + | * RISC-V 108MHz | ||

| + | * 64KB Flash/20KB RAM | ||

| + | * up to 26 I/O | ||

| + | * SysTick 24bit Timer x1 | ||

| + | * WDG x2, RTC x1 | ||

| + | * I2C x1; SPI x1; USART x2; CAN2.0 x2; | ||

| + | * USB OTG | ||

| + | * 12bit ADC x2(10 ch) | ||

| + | * 12bit DAC x2 | ||

| + | * QFN36, 6x6mm | ||

| + | |||

| + | [[文件:GD32VF103-QFN36.png]] | ||

<br> | <br> | ||

| + | |||

| + | === GD32VF103TBU6 === | ||

| + | |||

| + | * RISC-V 108MHz | ||

| + | * 128KB Flash/32KB RAM | ||

| + | * up to 26 I/O | ||

| + | * SysTick 24bit Timer x1 | ||

| + | * WDG x2, RTC x1 | ||

| + | * I2C x1; SPI x1; USART x2; CAN2.0 x2; | ||

| + | * USB OTG | ||

| + | * 12bit ADC x2(10 ch) | ||

| + | * 12bit DAC x2 | ||

| + | * QFN36, 6x6mm | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == Boot modes == | ||

| + | |||

| + | At startup, boot pins are used to select one of three boot options: | ||

| + | |||

| + | * Boot from main Flash memory (default) | ||

| + | * Boot from system memory | ||

| + | * Boot from on-chip SRAM | ||

| + | |||

| + | In default condition, boot from main Flash memory is selected. The boot loader is located in the internal boot ROM memory (system memory). | ||

| + | |||

| + | It is used to reprogram the Flash memory by using USART0 (PA9 and PA10) or USART1 (PA14 and PA15 or PA2 and PA3) | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == Toolchain == | ||

| + | |||

| + | === OpenOCD === | ||

| + | |||

| + | * [https://www.bilibili.com/read/cv8901530 用 OpenOCD 烧写 GD32E230] | ||

| + | |||

| + | * https://blog.csdn.net/weixin_39282203/article/details/104517912 | ||

| + | |||

| + | * https://www.e-learn.cn/topic/3447967 | ||

| + | |||

| + | <br><br><br><br> | ||

2021年10月9日 (六) 14:53的最后版本

目录 |

[编辑] 1 Overview

[编辑] 2 ARM

[编辑] 2.1 GD32E230G8U6

- 32 bit Cortex®-M23 Core, up to 72MHz

- 64KB Flash, 8KB RAM; G6U6 (32KB/6KB)

- I2C x2; SPI x2; USART x2

- RTC x1

- GPIO x23

- ADC x1

- 1.8V ~ 3.6V, 5V 容忍 I/O

- QFN28, 4x4mm

- GD32E230xx datasheet

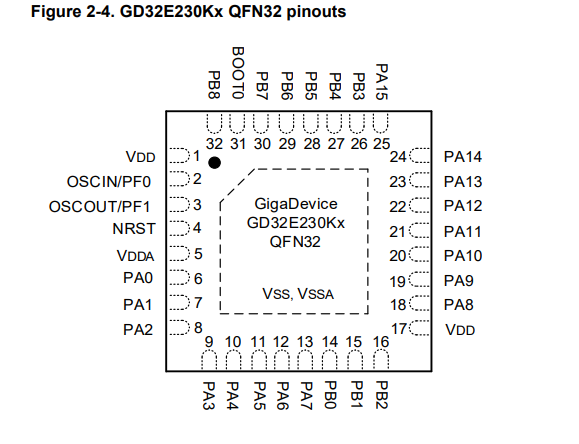

[编辑] 2.2 GD32E230K8U6

- 32 bit Cortex®-M23 Core, up to 72MHz

- 64KB Flash, 8KB RAM; K6U6 (32KB/6KB)

- I2C x2; SPI x2; USART x2

- RTC x1

- GPIO x23

- ADC x1

- 1.8V ~ 3.6V, 5V 容忍I/O

- QFN32, 5x5mm

- GD32E230xx datasheet

[编辑] 3 RISC-V

http://gd32mcu.com/cn/product/risc

[编辑] 3.1 GD32VF103T8U6

- RISC-V 108MHz

- 64KB Flash/20KB RAM

- up to 26 I/O

- SysTick 24bit Timer x1

- WDG x2, RTC x1

- I2C x1; SPI x1; USART x2; CAN2.0 x2;

- USB OTG

- 12bit ADC x2(10 ch)

- 12bit DAC x2

- QFN36, 6x6mm

[编辑] 3.2 GD32VF103TBU6

- RISC-V 108MHz

- 128KB Flash/32KB RAM

- up to 26 I/O

- SysTick 24bit Timer x1

- WDG x2, RTC x1

- I2C x1; SPI x1; USART x2; CAN2.0 x2;

- USB OTG

- 12bit ADC x2(10 ch)

- 12bit DAC x2

- QFN36, 6x6mm

[编辑] 4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from main Flash memory (default)

- Boot from system memory

- Boot from on-chip SRAM

In default condition, boot from main Flash memory is selected. The boot loader is located in the internal boot ROM memory (system memory).

It is used to reprogram the Flash memory by using USART0 (PA9 and PA10) or USART1 (PA14 and PA15 or PA2 and PA3)

[编辑] 5 Toolchain

[编辑] 5.1 OpenOCD