K210

来自Jack's Lab

(版本间的差异)

(→Overview) |

(→Overview) |

||

| 第38行: | 第38行: | ||

* Watchdog Timer (WDT) x1 | * Watchdog Timer (WDT) x1 | ||

| + | |||

| + | * JTAG | ||

<br><br> | <br><br> | ||

2018年10月29日 (一) 10:45的版本

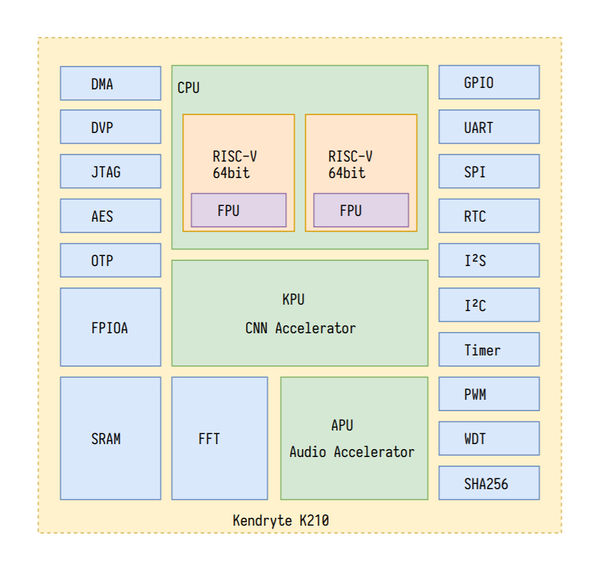

1 Overview

- 64-bit RISC-V CPU Dual-Core, up to 400MHz

- IMAFDC (RV64GC) ISA extension

- Hardware FPU (Float Point Unit), Double Precision

- 32 KB I-Cache per core

- 32 KB D-Cache per core

- 8MB On-Chip SRAM

- 128Kbit One-Time Programmable Memory (OTP)

- Read Only Memory (ROM)

- DMA

- Neural Network Accelerator (KPU)

- Audio Accelerator (APU)

- FFT Accelerator

- SHA256 Accelerator

- AES Accelerator

- DVP x1

- UART x4

- GPIO x40

- I2C x3

- SPI x4

- I2S x3

- PWM x1

- Timer x3

- RTC x1

- Watchdog Timer (WDT) x1

- JTAG

2 Datasheet

3 Reference