ASR650x

来自Jack's Lab

目录 |

1 ASR6505

- STM8L152

- Up to 16MHz

- 4KB RAM (0x0000 ~ 0x0FFF, including 513B stack)

- 2KB EEPROM (0x1000 ~ 0x1FFF)

- 64KB Flash (0x8080 ~ 0x1 7FFF)

- SPI x1, I2C x1, UART x2

- GPIO x30, ADC x3, SWIM x1

- 85mA @22dBm, 50mA@17dBm, 40mA@14dBm

- SX1262

- 2.4V to 3.7V (3.9V max) Power supply

- Sleep mode: 1uA without RTC, 1.6uA with RTC

- QFN68, 8x8mm

2 ASR6501

2.1 Overview

- PSoC 4100S Plus MCU

- 48 MHz ARM Cortex-M0+ Core

- up to 128kbytes of Flash memory and 16Kbytes of SRAM

- 6x configurable GPIOs, 1xI2C, 1xUART, 1xSWD

- 8-Channel DMA engine

- 12-bit 1Msps SAR ADC with differential and single-ended

- 32.768kHz External Watch Crystal Oscillator

- 4-33MHz External Crystal Oscillator for MCU (Optional)

- 32MHz External Crystal Oscillator for LoRa Radio

- Internal High frequency (48MHz) RC oscillator

- Internal Low frequency (40kHz) RC oscillator

- Internal PLL to generate 48MHz clock

- 1.71V to 5.5V Power supply

- Deep Sleep mode with 2.5uA

- SX1262

- 2.4V to 3.7V (3.9V max) Power supply

- Sleep mode: 2.7uA with RTC; 2uA without RTC

- QFN48 6x6mm

- 32-bit Arm® Cortex®-M0/M0+ PSoC® 4100 Intelligent Analog MCUs

- PSOC 4100s plus 256KB Datasheet

- PSOC 4100S Plus DatasheetENCN

- AN88619 - PSOC 4 HARDWARE DESIGN CONSIDERATIONS

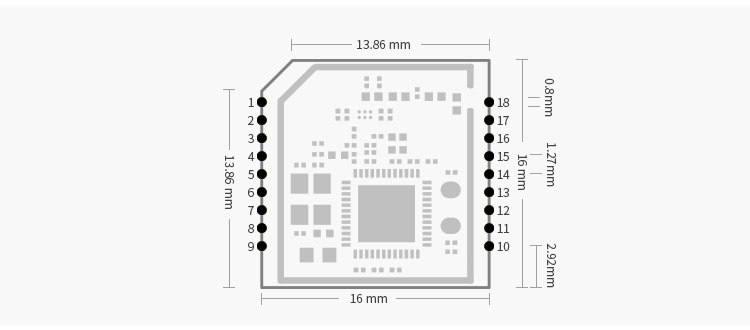

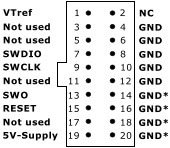

2.2 RF-AL42UH

* P1 GND 电源地 * P2 VDD, 电源输入,范围 2.8V ~ 3.6V DC * P3 ADC_IN,ADC输入脚,程序未启用,悬空 * P4 GPIO,MCU GPIO,悬空 * P5 AUX,MCU GPIO,悬空 * P6 SETA,MCU GPIO,悬空 * P7 RXD,UART 的 RX 信号 * P8 TXD,UART 的 TX 信号 * P9 SWD,SWD DATA引脚 * P10 SCLK,SWD CLK引脚 * P11 I2C_SCL,I2C引脚,程序未启用,悬空 * P12 I2C_SDA,I2C引脚,程序未启用,悬空 * P13 SETB,MCU GPIO,悬空 * P14 CTS,悬空 * P15 RTS,悬空 * P16 RESET,复位引脚,低电平有效。无须拉高(内部已经拉高) * P17 GND 电源地 * P18 天线接口

3 KitProg

3.1 PSoC Programmer

- https://www.cypress.com/products/psoc-programming-solutions

- https://www.cypress.com/file/505286/download

4 OpenOCD

STLink-V2:

comcat@AI-Workstation MINGW32 ~/work/nodetao/toolchain/openocd-cypress (master)

$ ./bin/openocd.exe -s ./scripts -f interface/stlink.cfg -c "source [find target/psoc4.cfg]; targets; shutdown"

Open On-Chip Debugger 0.10.0+dev-3.0.0.665 (2020-03-20-10:13)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : auto-selecting first available session transport "hla_swd". To override use 'transport select <transport>'.

adapter speed: 2000 kHz

** Test Mode acquire not supported by selected adapter

Info : The selected transport took over low-level target control. The results might differ compared to plain JTAG/SWD

TargetName Type Endian TapName State

-- ------------------ ---------- ------ ------------------ ------------

0* psoc4.cpu hla_target little psoc4.cpu unknown

shutdown command invoked

$ ./bin/openocd.exe -s ./scripts -f interface/stlink.cfg -c "program d:/BlinkyLED.hex verify reset; exit"

J-Link:

$ ./bin/openocd.exe -s ./scripts -f interface/jlink.cfg -c "transport select swd; source [find target/psoc4.cfg];"