ESP32 DAC

来自Jack's Lab

目录 |

1 Overview

Two DAC channel of ESP32:

- GPIO25 / RTC_GPIO6 / PIN_14

- GPIO26 / RTC_GPIO7 / PIN_15

2 Quick Start

In Linux:

2.1 Install ESP-IDF

$ sudo apt-get install git wget make libncurses-dev flex bison gperf python python-serial $ wget https://dl.espressif.com/dl/xtensa-esp32-elf-linux32-1.22.0-59.tar.gz $ mkdir -p toolchain $ tar zxf xtensa-esp32-elf-linux32-1.22.0-59.tar.gz -C toolchain $ export PATH=$PATH:`pwd`/toolchain/xtensa-esp32-elf/bin $ $ git clone --recursive git://github.com/icamgo/esp-idf.git $ export IDF_PATH=`pwd`/esp-idf

2.2 Compile

$ cd esp-idf/examples/09_dac_out $ make menuconfig $ make flash -j2

2.3 Upload

$ make flash

You need to press the RST buttom after uploading the firmware into flash. If you guys do not like to do this please patch the /path/to/esp-idf/components/esptool_py/esptool/esptool.py :

diff --git a/esptool.py b/esptool.py

index 755f4cb..ff92c91 100755

--- a/esptool.py

+++ b/esptool.py

@@ -197,6 +197,12 @@ class ESPLoader(object):

+ '\xc0'

self._port.write(buf)

+ def reset_to_app(self):

+ self._port.setDTR(False)

+ self._port.setRTS(True)

+ time.sleep(0.05)

+ self._port.setRTS(True)

+

""" Calculate checksum of a blob, as it is defined by the ROM """

@staticmethod

def checksum(data, state=ESP_CHECKSUM_MAGIC):

@@ -1421,7 +1427,6 @@ def dump_mem(esp, args):

sys.stdout.flush()

print 'Done!'

-

def write_flash(esp, args):

"""Write data to flash

"""

@@ -1503,6 +1508,7 @@ def write_flash(esp, args):

if args.verify:

print 'Verifying just-written flash...'

verify_flash(esp, args, header_block)

+ esp.reset_to_app()

def image_info(args):

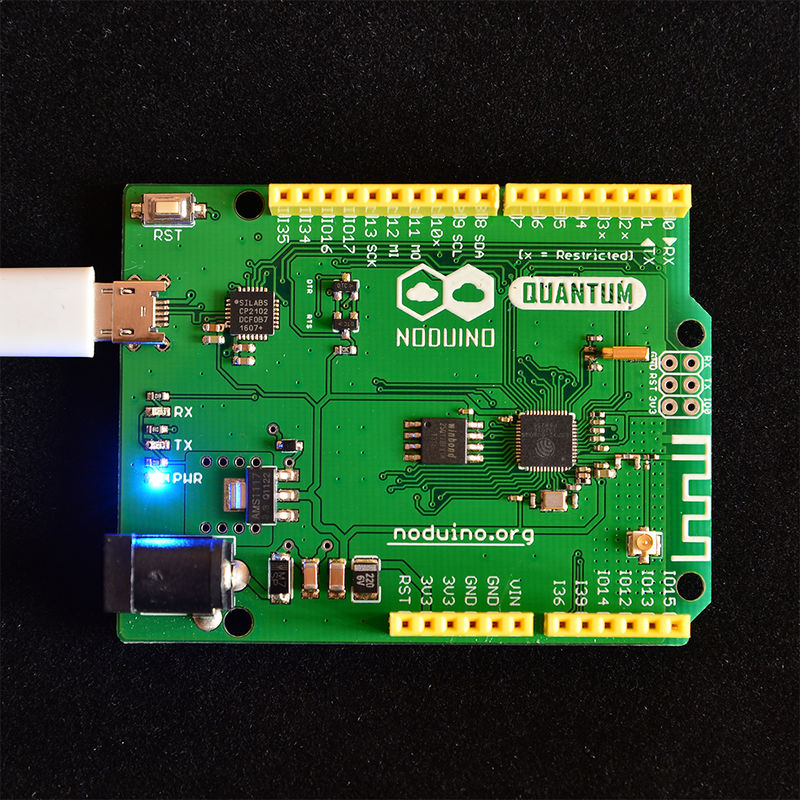

Then Quantum can reset to run your app automatically after uploading the firmware into flash

2.4 Connections

Use a wire to connect from Quantum_I35 to Quantum_D5_GPIO25 / Quantum_D6_GPIO26

The serial will output the voltage of the Quantum_D5_GPIO25 (DAC Channel 1) / Quantum_D6_GPIO26 (DAC channel 2)

3 API

static esp_err_t dac_pad_get_io_num(dac_channel_t channel, gpio_num_t *gpio_num)

{

RTC_MODULE_CHECK(channel < DAC_CHANNEL_MAX, "DAC Channel Err", ESP_ERR_INVALID_ARG);

switch (channel) {

case DAC_CHANNEL_1:

*gpio_num = 25;

break;

case DAC_CHANNEL_2:

*gpio_num = 26;

break;

default:

return ESP_ERR_INVALID_ARG;

}

return ESP_OK;

}

static esp_err_t dac_rtc_pad_init(dac_channel_t channel)

{

RTC_MODULE_CHECK(channel < DAC_CHANNEL_MAX, "DAC Channel Err", ESP_ERR_INVALID_ARG);

gpio_num_t gpio_num = 0;

dac_pad_get_io_num(channel, &gpio_num);

rtc_gpio_init(gpio_num);

rtc_gpio_output_disable(gpio_num);

rtc_gpio_input_disable(gpio_num);

rtc_gpio_pullup_dis(gpio_num);

rtc_gpio_pulldown_dis(gpio_num);

return ESP_OK;

}

static esp_err_t dac_out_enable(dac_channel_t channel)

{

if (channel == DAC_CHANNEL_1) {

portENTER_CRITICAL(&rtc_spinlock);

SET_PERI_REG_MASK(RTC_IO_PAD_DAC1_REG, RTC_IO_PDAC1_XPD_DAC | RTC_IO_PDAC1_DAC_XPD_FORCE);

portEXIT_CRITICAL(&rtc_spinlock);

} else if (channel == DAC_CHANNEL_2) {

portENTER_CRITICAL(&rtc_spinlock);

SET_PERI_REG_MASK(RTC_IO_PAD_DAC2_REG, RTC_IO_PDAC2_XPD_DAC | RTC_IO_PDAC2_DAC_XPD_FORCE);

portEXIT_CRITICAL(&rtc_spinlock);

} else {

return ESP_ERR_INVALID_ARG;

}

return ESP_OK;

}

esp_err_t dac_out_voltage(dac_channel_t channel, uint8_t dac_value)

{

RTC_MODULE_CHECK(channel < DAC_CHANNEL_MAX, "DAC Channel Err", ESP_ERR_INVALID_ARG);

portENTER_CRITICAL(&rtc_spinlock);

//Disable Tone

CLEAR_PERI_REG_MASK(SENS_SAR_DAC_CTRL1_REG, SENS_SW_TONE_EN);

//Disable Channel Tone

if (channel == DAC_CHANNEL_1) {

CLEAR_PERI_REG_MASK(SENS_SAR_DAC_CTRL2_REG, SENS_DAC_CW_EN1_M);

} else if (channel == DAC_CHANNEL_2) {

CLEAR_PERI_REG_MASK(SENS_SAR_DAC_CTRL2_REG, SENS_DAC_CW_EN2_M);

}

//Set the Dac value

if (channel == DAC_CHANNEL_1) {

SET_PERI_REG_BITS(RTC_IO_PAD_DAC1_REG, RTC_IO_PDAC1_DAC, dac_value, RTC_IO_PDAC1_DAC_S); //dac_output

} else if (channel == DAC_CHANNEL_2) {

SET_PERI_REG_BITS(RTC_IO_PAD_DAC2_REG, RTC_IO_PDAC2_DAC, dac_value, RTC_IO_PDAC2_DAC_S); //dac_output

}

portEXIT_CRITICAL(&rtc_spinlock);

//dac pad init

dac_rtc_pad_init(channel);

dac_out_enable(channel);

return ESP_OK;

}