基于忆阻器的DLA

(→参考文献) |

|||

| (未显示1个用户的3个中间版本) | |||

| 第8行: | 第8行: | ||

先前的DNN加速器主要是GPU、FPGA、ASIC为主,其中以ASIC的能效最好,以ASIC为例,大多数的DNN加速器作为一个co-processor出现,这样带来的问题是processor需要频繁跟主存进行数据交换,造成大量time-consuming和energy-consuming,寒武纪的DianNao在DRAM访存上消耗了整体95%的功耗。因此越来越多的方案采用大容量的片上SRAM来减少processor访存DRAM,即使这样,还不能解决输入和输出数据传输造成的功耗,而且片上SRAM的功耗也不少。所以,学术界提出了ReRAM Crossbar-based Accelerator for DNN,ReRAM可以说在这方面有天然的优势,集存储和计算功能于一身,灵活的可配置特性,基于ReRAM的DLA理论上可以提供很高的能效,这点可以从PRIME的设计方案中得知。同时将DRAM的读写速度与SSD的非易失性结合于一身,这也是ReRAM替代DRAM成为主存的潜力,这些优点我们暂且不说,接下来主要讨论ReRAM作为DNN加速器的潜力。 | 先前的DNN加速器主要是GPU、FPGA、ASIC为主,其中以ASIC的能效最好,以ASIC为例,大多数的DNN加速器作为一个co-processor出现,这样带来的问题是processor需要频繁跟主存进行数据交换,造成大量time-consuming和energy-consuming,寒武纪的DianNao在DRAM访存上消耗了整体95%的功耗。因此越来越多的方案采用大容量的片上SRAM来减少processor访存DRAM,即使这样,还不能解决输入和输出数据传输造成的功耗,而且片上SRAM的功耗也不少。所以,学术界提出了ReRAM Crossbar-based Accelerator for DNN,ReRAM可以说在这方面有天然的优势,集存储和计算功能于一身,灵活的可配置特性,基于ReRAM的DLA理论上可以提供很高的能效,这点可以从PRIME的设计方案中得知。同时将DRAM的读写速度与SSD的非易失性结合于一身,这也是ReRAM替代DRAM成为主存的潜力,这些优点我们暂且不说,接下来主要讨论ReRAM作为DNN加速器的潜力。 | ||

| + | |||

| + | <br> | ||

== Why ReRAM == | == Why ReRAM == | ||

| 第38行: | 第40行: | ||

1、首先是2016 ISCA的论文ISAAC的方案,后来清华大学的团队又在ISAAC的基础做了改进,这两篇文章就放在一起讨论,ISAAC的整体架构如下图所示,ISAAC的顶层由一些tiles组成,这些tiles通过网状结构互联,每一个tile里面包括一些in-situ multiply-accumulate(IMA) units、输出寄存器、shift-and-add、sigmoid、and max-pool units。每一个IMA 有一些 crossbar arrays 和 ADCs, connected with a shared bus. 同时IMA 也有input/output registers 和 shift-and-add units。这个架构具体是怎么计算的哪?ISAAC把这些tiles按网络的层分开,网络的每一个layer由专门的一些tiles负责计算。 | 1、首先是2016 ISCA的论文ISAAC的方案,后来清华大学的团队又在ISAAC的基础做了改进,这两篇文章就放在一起讨论,ISAAC的整体架构如下图所示,ISAAC的顶层由一些tiles组成,这些tiles通过网状结构互联,每一个tile里面包括一些in-situ multiply-accumulate(IMA) units、输出寄存器、shift-and-add、sigmoid、and max-pool units。每一个IMA 有一些 crossbar arrays 和 ADCs, connected with a shared bus. 同时IMA 也有input/output registers 和 shift-and-add units。这个架构具体是怎么计算的哪?ISAAC把这些tiles按网络的层分开,网络的每一个layer由专门的一些tiles负责计算。 | ||

| + | |||

[[文件:Reram-dla-03.jpg]] | [[文件:Reram-dla-03.jpg]] | ||

| + | |||

AEPE在ISAAC的基础上做了进一步的改进,主要针对优化ISAAC的面积和功耗,AEPE减少了一些on-chip buffer和on-chip network来改善面积,通过使所有列XBs共用一列DACs来减少DACs,同时对ADCs的精度和功耗做trade-off来减少功耗,优化后的结构如下图所示。增加Reg Buffer来减少eDRAM的带宽,提高数据复用,减少功耗。AEPE的实验结果显示能效增加了2.71x,面积减少了2.41x,精度只降低了0.5%。 | AEPE在ISAAC的基础上做了进一步的改进,主要针对优化ISAAC的面积和功耗,AEPE减少了一些on-chip buffer和on-chip network来改善面积,通过使所有列XBs共用一列DACs来减少DACs,同时对ADCs的精度和功耗做trade-off来减少功耗,优化后的结构如下图所示。增加Reg Buffer来减少eDRAM的带宽,提高数据复用,减少功耗。AEPE的实验结果显示能效增加了2.71x,面积减少了2.41x,精度只降低了0.5%。 | ||

| + | |||

[[文件:Reram-dla-04.jpg]] | [[文件:Reram-dla-04.jpg]] | ||

| + | |||

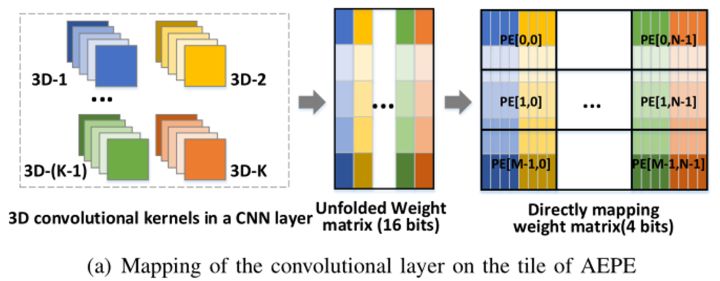

CNN layer在tiles里的mapping如下图a所示,通过把CNN一个layer的3D卷积核展开为一个权值矩阵,每一个3D卷积核的所有权值保存在unfolded weight matrix的每一列,因为一个ReRAM cell不够存储16bit的权值,AEPE以4bit的resolution把16bit的权值转化为直接映射权值矩阵,这样就可以通过分割矩阵直接mapping到ReRAM crossbars之中。 | CNN layer在tiles里的mapping如下图a所示,通过把CNN一个layer的3D卷积核展开为一个权值矩阵,每一个3D卷积核的所有权值保存在unfolded weight matrix的每一列,因为一个ReRAM cell不够存储16bit的权值,AEPE以4bit的resolution把16bit的权值转化为直接映射权值矩阵,这样就可以通过分割矩阵直接mapping到ReRAM crossbars之中。 | ||

| + | |||

[[文件:Reram-dla-05.jpg]] | [[文件:Reram-dla-05.jpg]] | ||

| + | |||

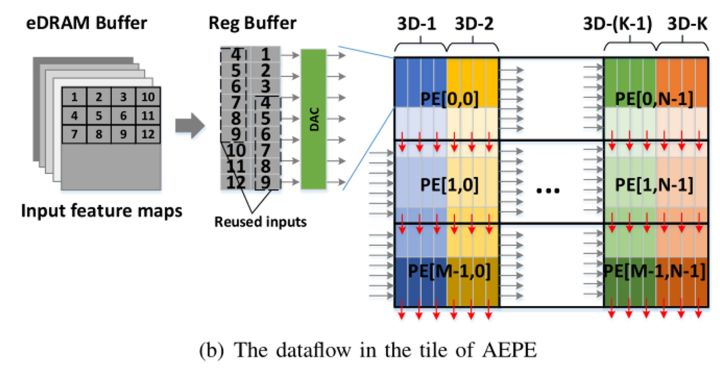

AEPE的Dataflow结构如下图b所示,可以充分的实现数据复用。原始的输入特征图像背包存在eDRAM buffer中,ping-pong寄存器buffer服务于当前PE阵列的计算和存储下一步卷积计算的输入。这里实现了三种数据复用,1)ping-pong寄存器数据的复用,2)每一行的PE复用同一批数据,3)每一列的PE复用卷积输出的partial sums | AEPE的Dataflow结构如下图b所示,可以充分的实现数据复用。原始的输入特征图像背包存在eDRAM buffer中,ping-pong寄存器buffer服务于当前PE阵列的计算和存储下一步卷积计算的输入。这里实现了三种数据复用,1)ping-pong寄存器数据的复用,2)每一行的PE复用同一批数据,3)每一列的PE复用卷积输出的partial sums | ||

| + | |||

[[文件:Reram-dla-06.jpg]] | [[文件:Reram-dla-06.jpg]] | ||

| + | |||

分析到这里,我们可以发现ReRAM确实很适合用来做矩阵向量乘法,抛开ReRAM介质,AEPE和IASSC的顶层架构,其实和传统的Dataflow结构有点相似,都有Memory Hierarchy的思想在里面,感觉除了底层PE由ReRAM组成,还没有完全抛开Dataflow的架构,同时基于ReRAM的DLA必须包含一堆DACs和ADCs,这也在一定程度上影响了面积和功耗,ISAAC只做到了380.7GOPs/W的能效,AEPE大概为1TGOPs/W多一点 | 分析到这里,我们可以发现ReRAM确实很适合用来做矩阵向量乘法,抛开ReRAM介质,AEPE和IASSC的顶层架构,其实和传统的Dataflow结构有点相似,都有Memory Hierarchy的思想在里面,感觉除了底层PE由ReRAM组成,还没有完全抛开Dataflow的架构,同时基于ReRAM的DLA必须包含一堆DACs和ADCs,这也在一定程度上影响了面积和功耗,ISAAC只做到了380.7GOPs/W的能效,AEPE大概为1TGOPs/W多一点 | ||

| 第63行: | 第73行: | ||

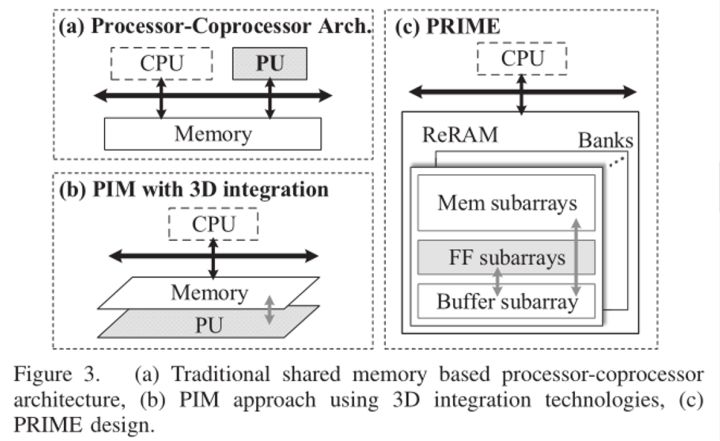

如下图所示,比较了传统DLA、processing in memory(PIM)和PRINME的区别,传统的DLA和PIM结构都需要额外的processing units (PU),而PRIME不需要。PRIME被设计为三个不同区域的bank,分别代表memory (Mem) subarrays, full function(FF) subarrays, and Buffer subarrays,Mem subarrays只存储数据,FF subarrays既可以做运算又可以做存储,Buffer subarrays作为FF subarrays的数据缓存,不做数据缓存的时候可以用来做常规的memory,Mem和Buffer subarrays通过私有的端口紧贴着与FF subarrays相连,这样buffer存取就不会消耗Mem subarrays的带宽。 | 如下图所示,比较了传统DLA、processing in memory(PIM)和PRINME的区别,传统的DLA和PIM结构都需要额外的processing units (PU),而PRIME不需要。PRIME被设计为三个不同区域的bank,分别代表memory (Mem) subarrays, full function(FF) subarrays, and Buffer subarrays,Mem subarrays只存储数据,FF subarrays既可以做运算又可以做存储,Buffer subarrays作为FF subarrays的数据缓存,不做数据缓存的时候可以用来做常规的memory,Mem和Buffer subarrays通过私有的端口紧贴着与FF subarrays相连,这样buffer存取就不会消耗Mem subarrays的带宽。 | ||

| + | |||

[[文件:Reram-dla-07.jpg]] | [[文件:Reram-dla-07.jpg]] | ||

| + | |||

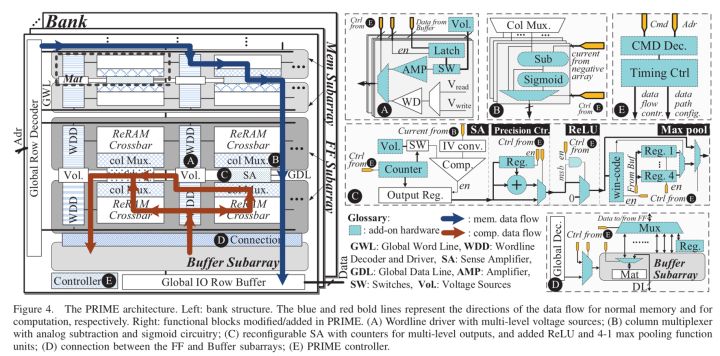

PRIME的微架构如下图所示,主要由A、B、C、D、E五个组件和Mem、FF、Buffer subarrays组成: | PRIME的微架构如下图所示,主要由A、B、C、D、E五个组件和Mem、FF、Buffer subarrays组成: | ||

| + | |||

[[文件:Reram-dla-08.jpg]] | [[文件:Reram-dla-08.jpg]] | ||

| + | |||

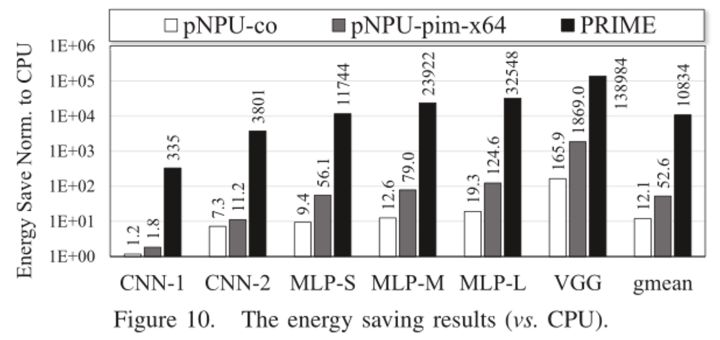

A 表示Decoder和Driver,用于控制输入电压、驱动模拟信号;B表示Column Multiplexer,用于支持NN的计算,包含subtraction unit和non- linear threshold (sigmoid) unit两个模拟单元,每个bitline上连接有一个multiplexer用于切换FF subarrays的存储和计算模式;C表示Sense Amplifier,用于支持不同精度的计算,同时集成ReLU、Max pool等操作;D表示Buffer Connection,用于连接Buffer subarrays和FF subarrays;E表示PRIME controller,用于指令译码和提供FF subarrays相关电路的控制信号,最后贴上几张PRIME的Evaluation图,pNPU-co指的是DianNao作为co-processor的NPU solution | A 表示Decoder和Driver,用于控制输入电压、驱动模拟信号;B表示Column Multiplexer,用于支持NN的计算,包含subtraction unit和non- linear threshold (sigmoid) unit两个模拟单元,每个bitline上连接有一个multiplexer用于切换FF subarrays的存储和计算模式;C表示Sense Amplifier,用于支持不同精度的计算,同时集成ReLU、Max pool等操作;D表示Buffer Connection,用于连接Buffer subarrays和FF subarrays;E表示PRIME controller,用于指令译码和提供FF subarrays相关电路的控制信号,最后贴上几张PRIME的Evaluation图,pNPU-co指的是DianNao作为co-processor的NPU solution | ||

| + | |||

[[文件:Reram-dla-09.jpg]] | [[文件:Reram-dla-09.jpg]] | ||

| + | |||

<br><br> | <br><br> | ||

| 第78行: | 第94行: | ||

== 参考文献 == | == 参考文献 == | ||

| − | + | * PRIME: A Novel Processing-in-memory Architecture for Neural Network Computation in ReRAM-based Main Memory | |

| − | + | * T. Chen et al., “DianNao: A small-footprint high-throughput accelerator for ubiquitous machine-learning,”in Proc. ASPLOS, 2014. | |

| − | + | * ISAAC: A Convolutional Neural Network Accelerator with In-Situ Analog Arithmetic in Crossbars | |

| − | + | * AEPE: An Area and Power Efficient ReRAM Crossbar-based Accelerator for Deep CNNs | |

| + | |||

| + | <br><br> | ||

| + | <br><br> | ||

| + | <br><br> | ||

| + | <br><br> | ||

| + | <br><br> | ||

| + | <br><br> | ||

2018年5月17日 (四) 18:37的最后版本

这是 Matery Allen 在该领域的文献综述,原文链接:https://zhuanlan.zhihu.com/p/33351291?utm_source=weibo&utm_medium=social&utm_oi=33945362104320

目录 |

[编辑] 1 申明

By Matery Allen

最近导师让调研总结一下关于DLA的研究,过程中注意到了ReRAM这个领域,通过几篇论文大概总结了一下,也是初次接触ReRAM相关的DLA,整个过程时间比较短,难免会有错误,还请见谅。

先前的DNN加速器主要是GPU、FPGA、ASIC为主,其中以ASIC的能效最好,以ASIC为例,大多数的DNN加速器作为一个co-processor出现,这样带来的问题是processor需要频繁跟主存进行数据交换,造成大量time-consuming和energy-consuming,寒武纪的DianNao在DRAM访存上消耗了整体95%的功耗。因此越来越多的方案采用大容量的片上SRAM来减少processor访存DRAM,即使这样,还不能解决输入和输出数据传输造成的功耗,而且片上SRAM的功耗也不少。所以,学术界提出了ReRAM Crossbar-based Accelerator for DNN,ReRAM可以说在这方面有天然的优势,集存储和计算功能于一身,灵活的可配置特性,基于ReRAM的DLA理论上可以提供很高的能效,这点可以从PRIME的设计方案中得知。同时将DRAM的读写速度与SSD的非易失性结合于一身,这也是ReRAM替代DRAM成为主存的潜力,这些优点我们暂且不说,接下来主要讨论ReRAM作为DNN加速器的潜力。

[编辑] 2 Why ReRAM

1、 Processing-in-memory (PIM):PIM is a promising solution to address the “memory wall” challenges for future computer systems;

2、 ReRAM的crossbar array structure可以很高效地完成矩阵向量乘法,这一点可以完美应用到DNN;

3、 Reconfigurable,支持多种large-scale DNNs,甚至可以支持SNN。

4、 ReRAM有更小的面积(high density storage)、更高的性能和更低的功耗;

5、 manufacture friendly with low cost,不需要复杂的逻辑集成设计或3D stacking;

[编辑] 3 ReRAM crossbar-based 矩阵向量乘法

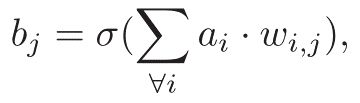

首先,说一下ReRAM crossbar architecture,如下图左所示,是一个具有子线和位线的阵列,为了增加密度和减少成本,可以做成multi-layer crossbar architecture和multi-level cell (MLC)。ReRAM是如何应用到Artificial neural networks (ANNs)上的,我们以2 × 2 ReRAM crossbar array为例来说明,如下图中所示,a i表示子线上的模拟输入电压,权重wi,j被编程到了crossbar array的cell里,每个位线的电流就是向量矩阵的乘积。

当然要在ReRAM上实现神经网络还需要一些其它电路结构,比如ADC、DAC、sigmoid unit等,一个完整的Vector-Matrix Multiplier如下图右所示。

[编辑] 4 ReRAM crossbar-based加速器的硬件实现

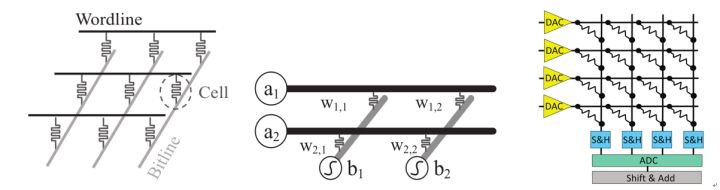

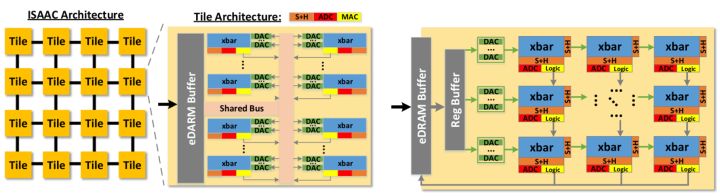

1、首先是2016 ISCA的论文ISAAC的方案,后来清华大学的团队又在ISAAC的基础做了改进,这两篇文章就放在一起讨论,ISAAC的整体架构如下图所示,ISAAC的顶层由一些tiles组成,这些tiles通过网状结构互联,每一个tile里面包括一些in-situ multiply-accumulate(IMA) units、输出寄存器、shift-and-add、sigmoid、and max-pool units。每一个IMA 有一些 crossbar arrays 和 ADCs, connected with a shared bus. 同时IMA 也有input/output registers 和 shift-and-add units。这个架构具体是怎么计算的哪?ISAAC把这些tiles按网络的层分开,网络的每一个layer由专门的一些tiles负责计算。

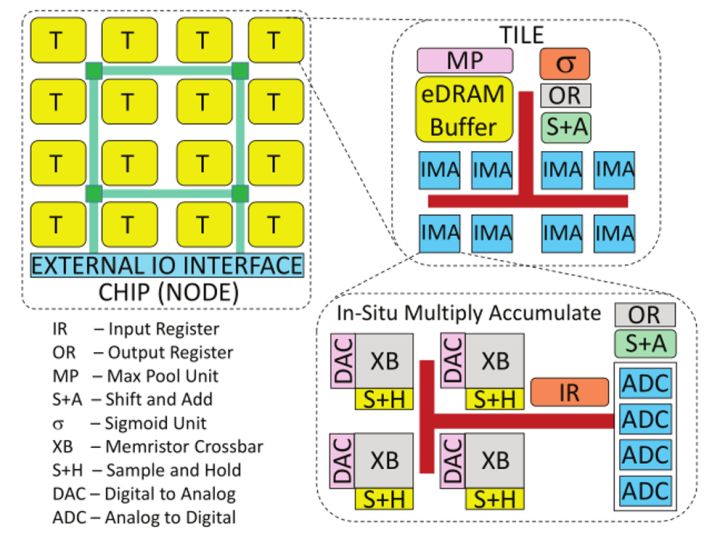

AEPE在ISAAC的基础上做了进一步的改进,主要针对优化ISAAC的面积和功耗,AEPE减少了一些on-chip buffer和on-chip network来改善面积,通过使所有列XBs共用一列DACs来减少DACs,同时对ADCs的精度和功耗做trade-off来减少功耗,优化后的结构如下图所示。增加Reg Buffer来减少eDRAM的带宽,提高数据复用,减少功耗。AEPE的实验结果显示能效增加了2.71x,面积减少了2.41x,精度只降低了0.5%。

CNN layer在tiles里的mapping如下图a所示,通过把CNN一个layer的3D卷积核展开为一个权值矩阵,每一个3D卷积核的所有权值保存在unfolded weight matrix的每一列,因为一个ReRAM cell不够存储16bit的权值,AEPE以4bit的resolution把16bit的权值转化为直接映射权值矩阵,这样就可以通过分割矩阵直接mapping到ReRAM crossbars之中。

AEPE的Dataflow结构如下图b所示,可以充分的实现数据复用。原始的输入特征图像背包存在eDRAM buffer中,ping-pong寄存器buffer服务于当前PE阵列的计算和存储下一步卷积计算的输入。这里实现了三种数据复用,1)ping-pong寄存器数据的复用,2)每一行的PE复用同一批数据,3)每一列的PE复用卷积输出的partial sums

分析到这里,我们可以发现ReRAM确实很适合用来做矩阵向量乘法,抛开ReRAM介质,AEPE和IASSC的顶层架构,其实和传统的Dataflow结构有点相似,都有Memory Hierarchy的思想在里面,感觉除了底层PE由ReRAM组成,还没有完全抛开Dataflow的架构,同时基于ReRAM的DLA必须包含一堆DACs和ADCs,这也在一定程度上影响了面积和功耗,ISAAC只做到了380.7GOPs/W的能效,AEPE大概为1TGOPs/W多一点

2、来自ISCA2016的一篇论文PRIME: A Novel Processing-in-memory Architecture for Neural Network Computation in ReRAM-based Main Memory让人眼前一亮,这是来自原文的一段话:“Our experimental results show that, compared with a state-of-the-art neural processing unit design, PRIME improves the performance by∼2360× and the energy consumption by ∼895×, across the evaluated machine learning benchmarks.”,要知道这里是在跟DianNao做对比,这数据让人震惊,下面我们主要讨论一下PRIME的实现。

PRIME不像前面讨论的ISAAC和AEPE,PRIME直接抛弃了AEPE里的eDRAM、Register buffer这样的存储结构设计,全部用ReRAM实现,设计了一种可变的内存计算架构:巧妙结合了ReRAM超高效加速神经网络的特点与内存计算的高效体系结构,充分利用了ReRAM既能作为存储器件,又能进行模拟计算的特性。比起一般的加速器结构或者单纯的内存计算结构,PRIME更灵活的可变结构能更有效利用资源,在需要神经网络计算的时候提供加速支持,而在其他时间提供更大的存储空间。同时,针对ReRAM计算精度受限的问题,PRIME提出了一套提升精度以达到神经网络计算要求的方法。在正常的ReRAM存储中,修改一部分存储的外围电路,使得这部分存储可以在“存储”状态和“神经网络加速器”状态之间灵活切换。其具体贡献包括:(1)存储外围电路设计,通过最大化复用存储和加速器的外围电路,最小化了需要在内存基础上添加的额外面积;(2)提出了一种克服ReRAM及其模拟计算精度偏低的方法;(3)提出了一整套的内存计算系统支持方案,并对大规模网络进行了仿真验证。

如下图所示,比较了传统DLA、processing in memory(PIM)和PRINME的区别,传统的DLA和PIM结构都需要额外的processing units (PU),而PRIME不需要。PRIME被设计为三个不同区域的bank,分别代表memory (Mem) subarrays, full function(FF) subarrays, and Buffer subarrays,Mem subarrays只存储数据,FF subarrays既可以做运算又可以做存储,Buffer subarrays作为FF subarrays的数据缓存,不做数据缓存的时候可以用来做常规的memory,Mem和Buffer subarrays通过私有的端口紧贴着与FF subarrays相连,这样buffer存取就不会消耗Mem subarrays的带宽。

PRIME的微架构如下图所示,主要由A、B、C、D、E五个组件和Mem、FF、Buffer subarrays组成:

A 表示Decoder和Driver,用于控制输入电压、驱动模拟信号;B表示Column Multiplexer,用于支持NN的计算,包含subtraction unit和non- linear threshold (sigmoid) unit两个模拟单元,每个bitline上连接有一个multiplexer用于切换FF subarrays的存储和计算模式;C表示Sense Amplifier,用于支持不同精度的计算,同时集成ReLU、Max pool等操作;D表示Buffer Connection,用于连接Buffer subarrays和FF subarrays;E表示PRIME controller,用于指令译码和提供FF subarrays相关电路的控制信号,最后贴上几张PRIME的Evaluation图,pNPU-co指的是DianNao作为co-processor的NPU solution

[编辑] 5 参考文献

- PRIME: A Novel Processing-in-memory Architecture for Neural Network Computation in ReRAM-based Main Memory

- T. Chen et al., “DianNao: A small-footprint high-throughput accelerator for ubiquitous machine-learning,”in Proc. ASPLOS, 2014.

- ISAAC: A Convolutional Neural Network Accelerator with In-Situ Analog Arithmetic in Crossbars

- AEPE: An Area and Power Efficient ReRAM Crossbar-based Accelerator for Deep CNNs