ESP32

(→First Glance) |

(→开发板) |

||

| (未显示1个用户的25个中间版本) | |||

| 第1行: | 第1行: | ||

| − | |||

| − | + | == Overview == | |

| − | + | ||

| − | + | ESP32,集成 2.4 GHz Wi-Fi 和蓝牙双模 SoC,台积电(TSMC) 40 nm工艺 | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

片内集成了天线开关、射频 Balun、 功率放大器、低噪放大器、过滤器以及电源管理模块,最小系统外部元器件少于 10 个 | 片内集成了天线开关、射频 Balun、 功率放大器、低噪放大器、过滤器以及电源管理模块,最小系统外部元器件少于 10 个 | ||

| 第64行: | 第11行: | ||

主要特性: | 主要特性: | ||

| − | * | + | * Xtensa 32-bit LX6 双核处理器,运算能力 600 DMIPS,主频 240MHz |

* 448 KB ROM (用于程序启动和内核功能调用) | * 448 KB ROM (用于程序启动和内核功能调用) | ||

* 520 KB SRAM (用于数据和指令存储) | * 520 KB SRAM (用于数据和指令存储) | ||

| 第70行: | 第17行: | ||

* QSPI 最多可连接 4 个 Flash / SRAM,每个 Flash 最大为 16 MB | * QSPI 最多可连接 4 个 Flash / SRAM,每个 Flash 最大为 16 MB | ||

* 供电电压:2.2V 到 3.6V | * 供电电压:2.2V 到 3.6V | ||

| + | * QFN48,5mm x 5mm 或者 6mm x 6mm | ||

| 第95行: | 第43行: | ||

* 蓝牙微微网(Piconet)和散射网(Scatternet) | * 蓝牙微微网(Piconet)和散射网(Scatternet) | ||

| − | + | <br> | |

=== 支持的 WiFi 特性 === | === 支持的 WiFi 特性 === | ||

| 第114行: | 第62行: | ||

* UMA 兼容和认证 | * UMA 兼容和认证 | ||

* 天线分集与选择 | * 天线分集与选择 | ||

| + | |||

| + | <br> | ||

| + | |||

| + | == 版本 == | ||

| + | |||

| + | {| class="wikitable" | ||

| + | !Identifier | ||

| + | !Processor cores | ||

| + | !Internal Flash memory (MB) | ||

| + | !Package size | ||

| + | !Description | ||

| + | |- | ||

| + | | ESP31B | ||

| + | | style="text-align:center" | 2 | ||

| + | | style="text-align:center" | 0 | ||

| + | | style="text-align:center" | 6×6 mm<sup>2</sup> | ||

| + | | Pre-release SoC used for beta testing; no longer available. | ||

| + | |- | ||

| + | | ESP32-D0WDQ6 | ||

| + | | style="text-align:center" | 2 | ||

| + | | style="text-align:center" | 0 | ||

| + | | style="text-align:center" | 6×6 mm<sup>2</sup> | ||

| + | | Initial production release chip of the ESP32 series. | ||

| + | |- | ||

| + | | ESP32‑D0WD | ||

| + | | style="text-align:center" | 2 | ||

| + | | style="text-align:center" | 0 | ||

| + | | style="text-align:center" | 5×5 mm<sup>2</sup> | ||

| + | | Smaller physical package variation similar to ESP32-D0WDQ6. | ||

| + | |- | ||

| + | | ESP32‑D2WD | ||

| + | | style="text-align:center" | 2 | ||

| + | | style="text-align:center" | 2 | ||

| + | | style="text-align:center" | 5×5 mm<sup>2</sup> | ||

| + | | 2 MiB (16 Mibit) embedded flash memory variation. | ||

| + | |- | ||

| + | | ESP32‑S0WD | ||

| + | | style="text-align:center" | 1 | ||

| + | | style="text-align:center" | 0 | ||

| + | | style="text-align:center" | 5×5 mm<sup>2</sup> | ||

| + | | Single-core processor variation. | ||

| + | |} | ||

| + | |||

| + | <br> | ||

| + | |||

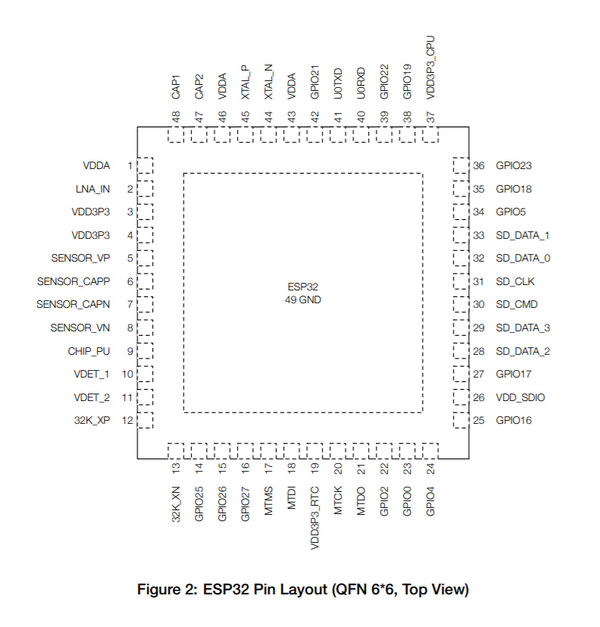

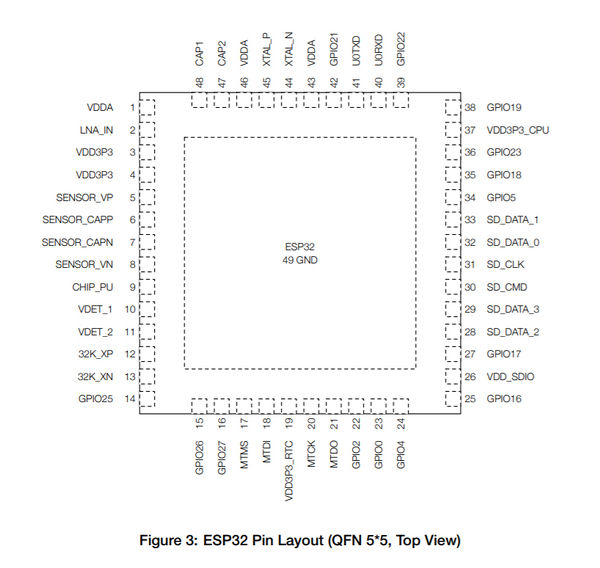

| + | == Pin Map == | ||

| + | |||

| + | [[文件:ESP32-6x6-pinmap.jpg | 600px]][[文件:ESP32-5x5-pinmap.jpg | 600px]] | ||

<br><br> | <br><br> | ||

| 第123行: | 第119行: | ||

[[文件:Esp32-block-diagram.jpg | 600px]] | [[文件:Esp32-block-diagram.jpg | 600px]] | ||

| + | |||

| + | * Xtensa Instruction Set Architecture: http://0x04.net/~mwk/doc/xtensa.pdf | ||

| + | * http://ip.cadence.com/uploads/533/Cadence_Tensillica_Xtensa_LX6_ds-pdf | ||

| + | |||

| + | <br><br> | ||

| + | |||

| + | == Xtensa ISA == | ||

| + | |||

| + | The Xtensa instruction set is designed to meet the diverse requirements of dataplane processing. | ||

| + | |||

| + | This 32-bit architecture features a compact 16- and 24-bit instruction set with modeless switching for maximum power efficiency and performance. | ||

| + | |||

| + | The base instruction set has 80 RISC instructions and includes a 32-bit ALU, up to 64 general-purpose 32-bit registers, and six special-purpose registers. | ||

| + | |||

| + | Using this instruction set, you can expect significant code size reductions that result in higher code density and better power dissipation. | ||

| + | |||

| + | |||

| + | * [[Xtensa GPR and ABI]] | ||

| + | * [[Xtensa Instruction Set]] | ||

| + | * [[Xtensa Exception]] | ||

| + | * [[Xtensa Memory]] | ||

<br><br> | <br><br> | ||

| 第156行: | 第173行: | ||

* 霍尔传感器 | * 霍尔传感器 | ||

| − | + | ||

| + | * [[ESP32 RTC]] ULP Co-processor | ||

* [[ESP32 I2S]] | * [[ESP32 I2S]] | ||

<br><br> | <br><br> | ||

| + | |||

| + | == First Glance == | ||

| + | |||

| + | <source lang=bash> | ||

| + | ets Jun 8 2016 00:22:57 | ||

| + | |||

| + | rst:0x10 (RTCWDT_RTC_RESET),boot:0x33 (SPI_FAST_FLASH_BOOT) | ||

| + | flash read err, 1000 | ||

| + | Falling back to built-in command interpreter. | ||

| + | OK | ||

| + | >ets Jun 8 2016 00:22:57 | ||

| + | |||

| + | rst:0x10 (RTCWDT_RTC_RESET),boot:0x33 (SPI_FAST_FLASH_BOOT) | ||

| + | flash read err, 1000 | ||

| + | Falling back to built-in command interpreter. | ||

| + | OK | ||

| + | >stop | ||

| + | OK | ||

| + | >about | ||

| + | ESP32 ROM Basic (c) 2016 Espressif Shanghai | ||

| + | Derived from TinyBasic Plus by Mike Field and Scott Lawrence | ||

| + | |||

| + | >help | ||

| + | A very Basic ROM console. Available commands/functions: | ||

| + | LIST | ||

| + | NEW | ||

| + | RUN | ||

| + | NEXT | ||

| + | LET | ||

| + | IF | ||

| + | GOTO | ||

| + | ...... | ||

| + | ...... | ||

| + | > | ||

| + | </source> | ||

| + | |||

| + | IO12(MTDI) Pull-up: | ||

| + | |||

| + | <source lang=bash> | ||

| + | ets Jun 8 2016 00:22:57 | ||

| + | |||

| + | rst:0x10 (RTCWDT_RTC_RESET),boot:0x33 (SPI_FAST_FLASH_BOOT) | ||

| + | flash read err, 1000 | ||

| + | Falling back to built-in command interpreter. | ||

| + | </source> | ||

| + | |||

| + | |||

| + | IO2 Pull-up: | ||

| + | |||

| + | <source lang=bash> | ||

| + | ets Jun 8 2016 00:22:57 | ||

| + | |||

| + | rst:0x10 (RTCWDT_RTC_RESET),boot:0x3b (SPI_FAST_FLASH_BOOT) | ||

| + | flash read err, 1000 | ||

| + | Falling back to built-in command interpreter. | ||

| + | </source> | ||

| + | |||

| + | |||

| + | IO12(MTDI) Pull-down: | ||

| + | |||

| + | <source lang=bash> | ||

| + | ets Jun 8 2016 00:22:57 | ||

| + | |||

| + | rst:0x10 (RTCWDT_RTC_RESET),boot:0x13 (SPI_FAST_FLASH_BOOT) | ||

| + | flash read err, 1000 | ||

| + | Falling back to built-in command interpreter. | ||

| + | </source> | ||

| + | |||

| + | |||

| + | IO2 Pull-up, IO0 Pull-down: | ||

| + | |||

| + | <source lang=bash> | ||

| + | ets Jun 8 2016 00:22:57 | ||

| + | |||

| + | rst:0x10 (RTCWDT_RTC_RESET),boot:0x2b (HSPI_FLASH_BOOT) | ||

| + | flash read err, 1000 | ||

| + | Falling back to built-in command interpreter. | ||

| + | </source> | ||

| + | |||

| + | |||

| + | |||

| + | --------------------- | ||

| + | |||

| + | IO0 Pull-down: | ||

| + | |||

| + | <source lang=bash> | ||

| + | >ets Jun 8 2016 00:22:57 | ||

| + | |||

| + | rst:0x10 (RTCWDT_RTC_RESET),boot:0x23 (DOWNLOAD_BOOT(UART0/UART1/SDIO_REI_REO_V2)) | ||

| + | waiting for download | ||

| + | </source> | ||

| + | |||

| + | |||

| + | IO0 and IO12(MTDI) Pull-down: | ||

| + | <source lang=bash> | ||

| + | ets Jun 8 2016 00:22:57 | ||

| + | |||

| + | rst:0x1 (POWERON_RESET),boot:0x3 (DOWNLOAD_BOOT(UART0/UART1/SDIO_REI_REO_V2)) | ||

| + | waiting for download | ||

| + | </source> | ||

| + | |||

| + | |||

<br><br> | <br><br> | ||

| + | |||

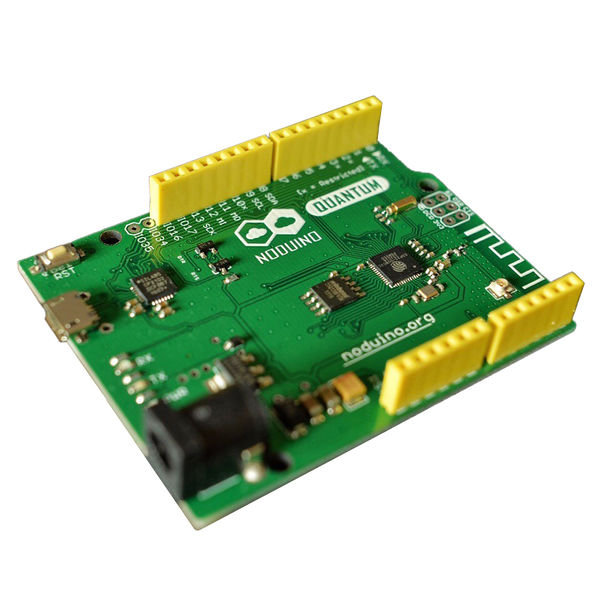

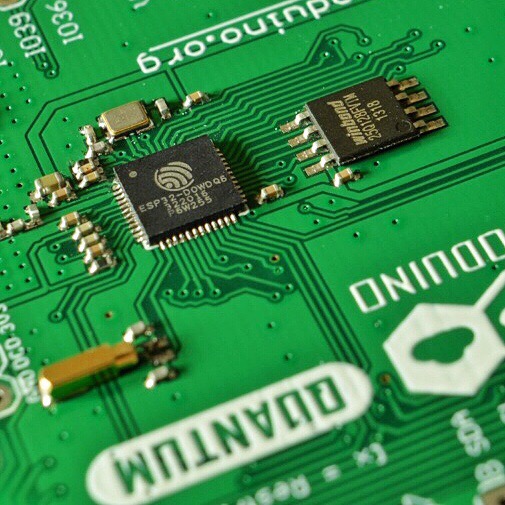

| + | == 开发板 == | ||

| + | |||

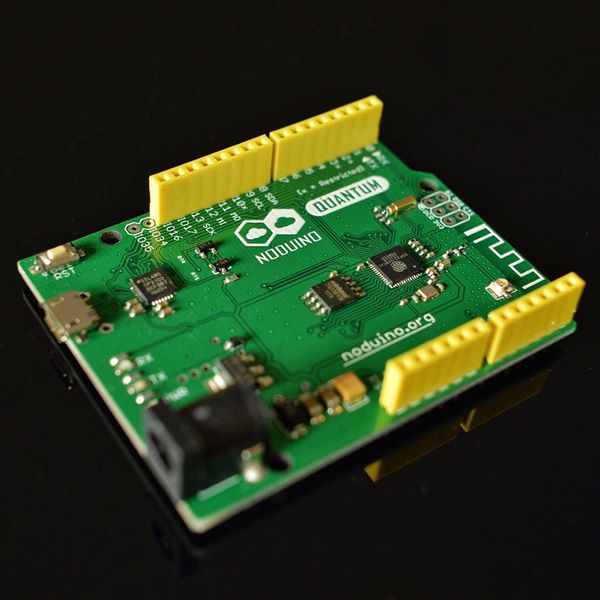

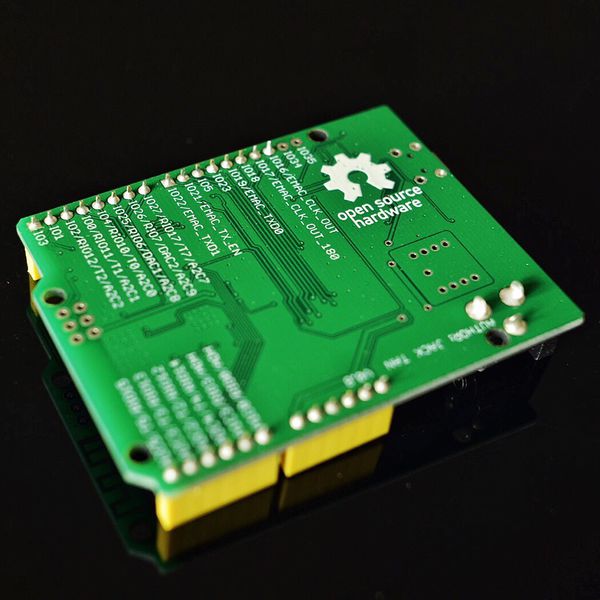

| + | [[文件:Quantum-6.jpg | 600px ]] | ||

| + | [[文件:Quantum-3.jpg | 600px ]] | ||

| + | [[文件:Quantum-4.jpg | 600px ]] | ||

| + | [[文件:Quantum-5.jpg | 600px ]] | ||

| + | |||

| + | |||

| + | * CP2102 USB to UART Chip | ||

| + | * ESP32 Bluetooth and WiFi SoC | ||

| + | * 40MHz Crystal (±10ppm, ±10ppm) | ||

| + | * 16MB SPI Flash | ||

| + | * 5V - 12V Power Supply | ||

| + | * FreeRTOS | ||

| + | |||

| + | |||

| + | 更多详细信息,移步: [[Noduino Quantum]] | ||

| + | |||

<br><br> | <br><br> | ||

<br><br> | <br><br> | ||

| − | |||

| − | |||

<br><br> | <br><br> | ||

<br><br> | <br><br> | ||

| − | |||

2018年10月24日 (三) 10:30的最后版本

目录 |

[编辑] 1 Overview

ESP32,集成 2.4 GHz Wi-Fi 和蓝牙双模 SoC,台积电(TSMC) 40 nm工艺

片内集成了天线开关、射频 Balun、 功率放大器、低噪放大器、过滤器以及电源管理模块,最小系统外部元器件少于 10 个

专为移动设备、可穿戴电子产品和物联网(IoT)应用而设计。超低功耗,内部具有精细分辨时钟门控、省电模式和动态电压调整等特性

主要特性:

- Xtensa 32-bit LX6 双核处理器,运算能力 600 DMIPS,主频 240MHz

- 448 KB ROM (用于程序启动和内核功能调用)

- 520 KB SRAM (用于数据和指令存储)

- RTC 中 16 KB SRAM

- QSPI 最多可连接 4 个 Flash / SRAM,每个 Flash 最大为 16 MB

- 供电电压:2.2V 到 3.6V

- QFN48,5mm x 5mm 或者 6mm x 6mm

- RTC 中 8 KB 的 SRAM,即 RTC 慢速存储器,可以在 Deep-sleep 模式下被协处理器访问

- RTC 中 8 KB 的 SRAM,即 RTC 快速存储器,可以在 Deep-sleep 模式下 RTC 启动时用于数据存储以 及被主 CPU 访问

- 1 kbit 的 EFUSE,其中 256 bits 为系统专用(MAC 地址和芯片设置);其余 768 bits 保留给用户应用,这 些应用包括 Flash 加密和芯片 ID

[编辑] 1.1 支持的蓝牙特性

- 蓝牙 v4.2 完整标准,包含传统蓝牙(BR/EDR)和低功耗蓝牙(BLE)

- 支持标准 Class-1、Class-2 和 Class-3,且无需外部功率放大器

- 增强的精准功率控制

- 输出功率高达 +10 dBm

- NZIF 接收器具有 -98 dBm 的 BLE 接收灵敏度

- 自适应跳频(AFH)

- 基于 SDIO / SPI / UART 接口的标准 HCI

- 速度高达 4 Mbps 的高速 UART HCI

- 服务发现协议(SDP),通用访问应用(GAP),安全管理协议(SMP)

- HID

- 可支持所有基于 GATT 的低功耗蓝牙应用

- BLE Beacon

- CVSD 和 SBC 音频编解码算法

- 蓝牙微微网(Piconet)和散射网(Scatternet)

[编辑] 1.2 支持的 WiFi 特性

- 802.11 b/g/n/e/i

- 802.11 n(2.4 GHz),速度高达 150 Mbps

- 802.11 e:QoS 机制实现无线多媒体技术

- 支持 WPA / WPA2 / WPA2-Enterprise / WPS 加密

- 基础结构型网络(Infrastructure BSS)Station 模式/ SoftAP 模式

- 802.11 i 安全特性:预认证和 TSN

- Beacon 自动监测/扫描

- Wi-Fi Direct(P2P)、P2P 发现、P2P GO 模式和 P2P 电源管理

- WMM-PS, UAPSD

- A-MPDU 和 A-MSDU 帧聚合技术

- UMA 兼容和认证

- 天线分集与选择

[编辑] 2 版本

| Identifier | Processor cores | Internal Flash memory (MB) | Package size | Description |

|---|---|---|---|---|

| ESP31B | 2 | 0 | 6×6 mm2 | Pre-release SoC used for beta testing; no longer available. |

| ESP32-D0WDQ6 | 2 | 0 | 6×6 mm2 | Initial production release chip of the ESP32 series. |

| ESP32‑D0WD | 2 | 0 | 5×5 mm2 | Smaller physical package variation similar to ESP32-D0WDQ6. |

| ESP32‑D2WD | 2 | 2 | 5×5 mm2 | 2 MiB (16 Mibit) embedded flash memory variation. |

| ESP32‑S0WD | 1 | 0 | 5×5 mm2 | Single-core processor variation. |

[编辑] 3 Pin Map

[编辑] 4 体系结构

ESP32 内部框图:

- Xtensa Instruction Set Architecture: http://0x04.net/~mwk/doc/xtensa.pdf

- http://ip.cadence.com/uploads/533/Cadence_Tensillica_Xtensa_LX6_ds-pdf

[编辑] 5 Xtensa ISA

The Xtensa instruction set is designed to meet the diverse requirements of dataplane processing.

This 32-bit architecture features a compact 16- and 24-bit instruction set with modeless switching for maximum power efficiency and performance.

The base instruction set has 80 RISC instructions and includes a 32-bit ALU, up to 64 general-purpose 32-bit registers, and six special-purpose registers.

Using this instruction set, you can expect significant code size reductions that result in higher code density and better power dissipation.

[编辑] 6 片内外设

- 12-bit SAR ADC,18 个通道

- 2 个 8-bit D/A 转换器

- 超低功耗前置模拟放大器

- 1 个 Host SD / eMMC / SDIO

- 1 个 Slave SDIO / SPI

- 带有专用 DMA 的以太网 MAC 接口,支持 IEEE 1588

- CAN 2.0

- 2 个 I2C

- 4 个 SPI

- 3 个 UART

- IR(TX / RX)

- 2 个 I2S

- 电机 PWM (3 路 16-bit 定时器产生 PWM 波形,每路 包含一对输出信号。3 个故障检测信号。3 个 even capture 信号。3 个同步信号)

- LED PWM,16 个通道(16 个独立的通道运行在 80MHz 的时钟或 RTC 时钟上。占空比精确度:16-bit)

- 10 个电容式触摸传感器

- 温度传感器

- 霍尔传感器

- ESP32 RTC ULP Co-processor

[编辑] 7 First Glance

ets Jun 8 2016 00:22:57 rst:0x10 (RTCWDT_RTC_RESET),boot:0x33 (SPI_FAST_FLASH_BOOT) flash read err, 1000 Falling back to built-in command interpreter. OK >ets Jun 8 2016 00:22:57 rst:0x10 (RTCWDT_RTC_RESET),boot:0x33 (SPI_FAST_FLASH_BOOT) flash read err, 1000 Falling back to built-in command interpreter. OK >stop OK >about ESP32 ROM Basic (c) 2016 Espressif Shanghai Derived from TinyBasic Plus by Mike Field and Scott Lawrence >help A very Basic ROM console. Available commands/functions: LIST NEW RUN NEXT LET IF GOTO ...... ...... >

IO12(MTDI) Pull-up:

ets Jun 8 2016 00:22:57 rst:0x10 (RTCWDT_RTC_RESET),boot:0x33 (SPI_FAST_FLASH_BOOT) flash read err, 1000 Falling back to built-in command interpreter.

IO2 Pull-up:

ets Jun 8 2016 00:22:57 rst:0x10 (RTCWDT_RTC_RESET),boot:0x3b (SPI_FAST_FLASH_BOOT) flash read err, 1000 Falling back to built-in command interpreter.

IO12(MTDI) Pull-down:

ets Jun 8 2016 00:22:57 rst:0x10 (RTCWDT_RTC_RESET),boot:0x13 (SPI_FAST_FLASH_BOOT) flash read err, 1000 Falling back to built-in command interpreter.

IO2 Pull-up, IO0 Pull-down:

ets Jun 8 2016 00:22:57 rst:0x10 (RTCWDT_RTC_RESET),boot:0x2b (HSPI_FLASH_BOOT) flash read err, 1000 Falling back to built-in command interpreter.

IO0 Pull-down:

>ets Jun 8 2016 00:22:57 rst:0x10 (RTCWDT_RTC_RESET),boot:0x23 (DOWNLOAD_BOOT(UART0/UART1/SDIO_REI_REO_V2)) waiting for download

IO0 and IO12(MTDI) Pull-down:

ets Jun 8 2016 00:22:57 rst:0x1 (POWERON_RESET),boot:0x3 (DOWNLOAD_BOOT(UART0/UART1/SDIO_REI_REO_V2)) waiting for download

[编辑] 8 开发板

- CP2102 USB to UART Chip

- ESP32 Bluetooth and WiFi SoC

- 40MHz Crystal (±10ppm, ±10ppm)

- 16MB SPI Flash

- 5V - 12V Power Supply

- FreeRTOS

更多详细信息,移步: Noduino Quantum