ESP8266

来自Jack's Lab

(版本间的差异)

(→概述) |

(→概述) |

||

| 第1行: | 第1行: | ||

== 概述 == | == 概述 == | ||

| + | |||

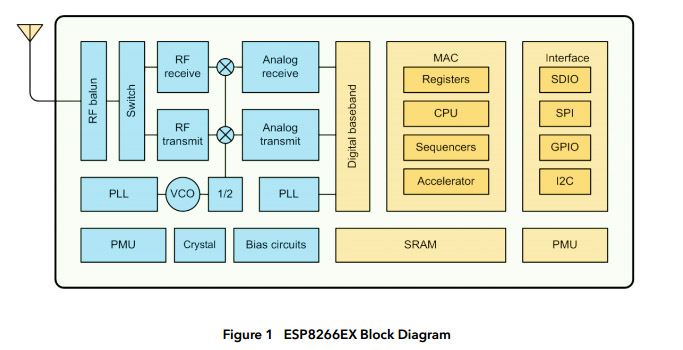

| + | ESP8266EX 集成:天线开关,RF balun,功率放大器,低噪放大器,过滤器,电源管理模块 | ||

| + | |||

| + | 仅需 7 个外围器件,就是一个完整的带 32bit MCU | ||

ESP8266 结构框图: | ESP8266 结构框图: | ||

| 第10行: | 第14行: | ||

=== MCU 体系结构 === | === MCU 体系结构 === | ||

| − | ;; Tensilica Xtensa LX3 32-bit RISC SOC clocked at 80 | + | ;; Tensilica Xtensa LX3 32-bit RISC SOC clocked at 80 MHz,It can also reach a maximum value of 160MHz |

| + | |||

| + | ;; Only 20% of MIPS has been occupied by the WiFi stack, the rest can all be used for user application programming and development. | ||

| + | |||

| + | ESP8266EX WiFi SoC is embedded with memory controller, including SRAM and ROM. MCU can visit the memory units through iBus, dBus, and AHB interfaces. All memory units can be visited upon request, while a memory arbiter will decide the running sequence according to the time when these requests are received by the processor. According to our current version of SDK provided, SRAM space that is available to users is assigned as below: | ||

| + | |||

| + | * RAM size is around 50 KB, that is to say, when ESP8266EX is working under the station mode and is connected to the router, programmable space accessible to user in heap and data section is around 50 KB.) | ||

| + | * There is no programmable ROM in the SoC, therefore, user program must be stored in an external SPI flash. | ||

[[文件:Tensilica-xtensalx3.jpg]] | [[文件:Tensilica-xtensalx3.jpg]] | ||

2015年9月23日 (三) 13:53的版本

目录 |

1 概述

ESP8266EX 集成:天线开关,RF balun,功率放大器,低噪放大器,过滤器,电源管理模块

仅需 7 个外围器件,就是一个完整的带 32bit MCU

ESP8266 结构框图:

内部 CPU (MCU) 使用 Tensilica’s L106 钻石系列32位内核处理器,带片上 SRAM

1.1 MCU 体系结构

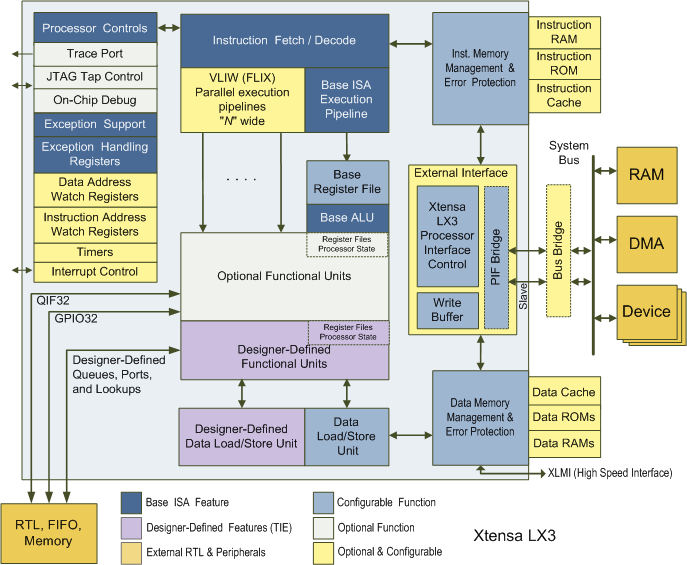

- Tensilica Xtensa LX3 32-bit RISC SOC clocked at 80 MHz,It can also reach a maximum value of 160MHz

- Only 20% of MIPS has been occupied by the WiFi stack, the rest can all be used for user application programming and development.

ESP8266EX WiFi SoC is embedded with memory controller, including SRAM and ROM. MCU can visit the memory units through iBus, dBus, and AHB interfaces. All memory units can be visited upon request, while a memory arbiter will decide the running sequence according to the time when these requests are received by the processor. According to our current version of SDK provided, SRAM space that is available to users is assigned as below:

- RAM size is around 50 KB, that is to say, when ESP8266EX is working under the station mode and is connected to the router, programmable space accessible to user in heap and data section is around 50 KB.)

- There is no programmable ROM in the SoC, therefore, user program must be stored in an external SPI flash.

- 32-bit ALU

- 16, 32 or 64 GPR

- six special purpose registers

- 80 base instructions

The Xtensa ISA employs 24-bit instructions with 16-bit narrow encodings for the most common instructions.

2 Quick Start

3 资源