UART 体系结构

目录 |

1 概述

UART:Universal Asynchronous Receiver Transmitter,通用异步收发器

即为嵌入式领域最为常说的串口。最常用的波特率为 9600bps、115200bps

“异步”是指不需要额外的时钟线进行数据的同步传输,是一种串行总线接口,只用两根线就可以完成数据的收发:一根线上发送数据,另一根线接收数据

发送和接受时,数据是逐位传输

2 逻辑层

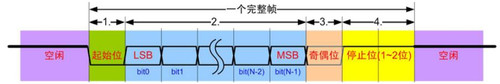

- 帧格式

由起始位、数据位、校验位和停止位组成

UART 空闲(IDLE)时(没有数据传递),总线为高电平(逻辑1)

开始数据传输时,首先发送起始位(低电平,逻辑0),然后再逐位传输数据(LSB --> MSB),数据传输完成后,有校验位则传输1位校验位,再传一位停止位(逻辑1,高电平)。至此,数据传输完成,UART 重回 IDLE 状态,总线上的电平为高

具体位解析:

* 起始位 (1位,必须)

起始位是TX告知RX,数据传输即将开始。而RX无论何时,只要检测到低电平,就开始逐位接收数据。

* 数据位

顾名思义,数据位是用来传输信息的。长度可以说5、6、7、8位。收/发双方需要在数据传输前,对双方的数据位作一致的定义。最常用的是 8 位

* 校验位 (1位,可选)

为了保证数据传输的安全性而设。不是强制的,距离短确定无干扰的环境,为提高传输速度,可不用此位。

在数据长距离传输时,UART使用 RS-232、RS-485 传输,在传输的导线较长时,如遇干扰,会导致传输的数据错误(1变0,0变1)。加上校验位的话,

接受端可做检验。如果校验出错,说明数据不可信,直接丢弃;校验通过的话,数据初步可信,进入下一级校验,通常在通信协议里再做一次校验

收/发双方,事先应商定好是否需要校验位。不需要,则罢;需要,则可选奇校验或偶校验

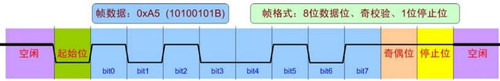

偶校验:数据位中的“1”的个数为偶数时,校验位为 0;数据位中的“1”的个数为奇数时,校验位为 1;即:保证数据位和校验位中1的个数为偶数

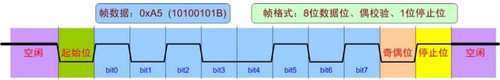

奇校验:数据位中的“1”的个数为偶数时,校验位为 1;数据位中的“1”的个数为奇数时,校验位为 0;即:保证数据位和校验位中1的个数为奇数

两个校验位的示例图:

* 停止位

停止位当然是告诉 RX 停止传输了。它的位数比较特别,可以说1位、1.5位、2位

停止位始终为逻辑 1 (高电平)

* 空闲位

TX 传输完成,RX 不能休息,其要始终盯着 URAT 总线上电平变化。。。

3 物理层

UART 传输信号线最少只要两根线,TX 和 RX

3.1 RS232

RS232: Recommended Standard 232

RS-232 标准(TIA-232) 由 TIA (Telecommunications Industry Association) 定义。其定义了接口的物理特性和电气特性。

RS-232 is practically identical to ITU V.24 (signal description and names) and V.28 (electrical)

RS232 is an Active LOW voltage driven interface and operates at +12V to -12V where:

- Signal = 1 (HIGH) < -3.0V (MARK) (-15V ~ -3V)

- Signal = 0 (LOW) > +3.0V (SPACE) (+3V ~ +15V)

除 TX 与 RX 线外,其还有多条其他的信号线:RTS, CTS, DSR, DTR, DCD, RI, GND 等

3.2 TTL

TTL:Transistor-Transistor Logic

单片机 (MCU) 内一般皆实现仅有 TX/RX 两根线的串口,通常称这类串口为 TTL Serial

- Signal = 1 (HIGH) +5V / +3.3V

- Signal = 0 (LOW) 0V

4 常见芯片

UART 的常见芯片:

- 8250 老芯片,始于 IBM XT,最高波特率应该是 9600bps

- 16450 最高波特率 38400bps,无收发缓存,收或发一个字节就要一次软件处理,高速下 CPU 负担会很重

- 16550A 最高波特率 115200bps,收发各有一个 32 字节的 FIFO Buffer,高速下,CPU负担低

目前在 PC 平台和嵌入式平台上,最常见的就是类 16550A 实现

5 参考