V831

来自Jack's Lab

目录 |

1 Overview

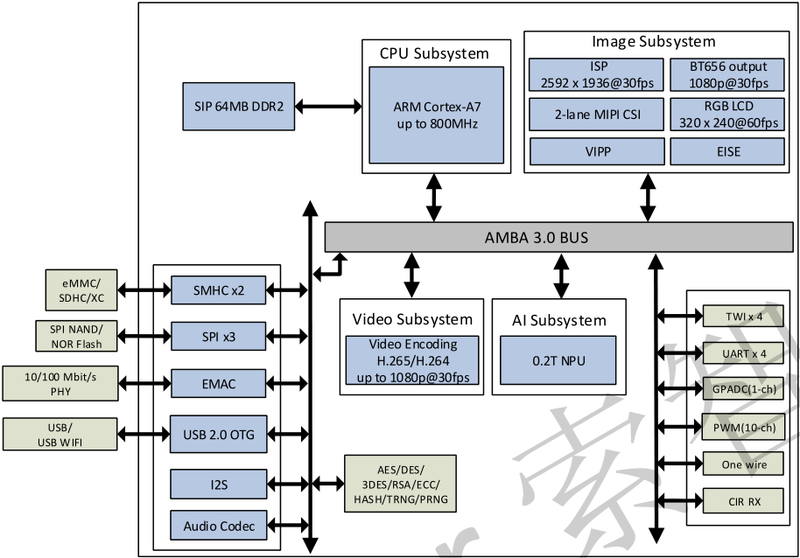

全志 V831

- Cortex-A7 单核,800MHz

- SIP 64MB DDR2

- 0.2T NPU

- TWI x4

- SPI x2

- SMHC x2

- GPADC x1

- Serial RGB, i8080

- 100M Ethernet with RGMII

- QFN88

2 Pinmap

- 36: PH14/JTAG_DI/MDIO/SPI1_CS0/TWI3_SDA

- 37: PH13/JTAG_DO/MDC/SPI1_MISO/TWI3_SCK

- 38: PH12/JTAG_CK/RMII_TXEN/SPI1_MOSI/TWI2_SDA

- 39: PH11/JTAG_MS/RMII_TXCK/SPI1_CLK/TWI2_SCK

- 40: PH10/RMII_TXD0/TWI3_SDA/UART0_RX

- 41: PH9/PWM_9/RMII_TXD1/TWI3_SCK/UART0_TX

- 42: PH8/PWM_8/RMII_RXER/UART0_RX/UART2_CTS

- 43: PH7/PWM_7/RMII_CRS_DV/UART0_TX/UART2_RTS

- 44: PH6/PWM_6/RMII_RXD0/TWI2_SDA/UART2_RX

- 45: VDD_SYS3

- 46: VCC18_IO

- 47: PH5/PWM_5/RMII_RXD1/TWI2_SCK/UART2_TX

- 48: PH4/PWM_4/I2S0_DIN/SPI1_CS1/ONEWIRE

- 49: PH3/PWM_3/I2S0_DOUT/SPI1_CS0/UART3_RTS

- 50: PH2/PWM_2/I2S0_LRCK/SPI1_MISO/UART3_CTS

- 51: PH1/PWM_1/I2S0_BCLK/SPI1_MOSI/UART3_RX

- 52: PH0/PWM_0/I2S0_MCLK/SPI1_CLK/UART3_TX

- 53: VCC_IO

- 54: GPADC0

- 55: AVCC

- 56: LINEOUTP

- 57: VRA1

- 58: AGND

- 59: VRA2

- 60: MICIN1N

- 61: MICIN1P

- 62: VDD_SYS4

- 63: PC0/SPI0_CLK

- 64: PC1/SPI0_CS0

- 65: PC2/SPI0_MOSI

- 66: PC3/SPI0_MISO

- 67: PC4/SPI0_WP

- 68: PC5/SPI0_HOLD

- 69: MCSIA_D0N

- 70: MCSIA_D0P

- 71: MCSIA_D1P

- 72: MCSIA_D1N

- 73: MCSIA_CKN

- 74: MCSIA_CKP

- 75: VCC_MCSI

- 76: USB0_DP

- 77: USB0_DM

- 78: PI0/CSI_MASTERCLK0

- 79: PI1/CSI_SM_HS/TWI1_SCK

- 80: PI2/CSI_SM_VS/TWI1_SDA

- 81: PD1/LCD_D3/PWM_0/RMII_RXD1

- 82: PD2/LCD_D4/PWM_1/RMII_RXD0

- 83: PD3/LCD_D5/PWM_2/RMII_CRS_DV

- 84: PD4/LCD_D6/PWM_3/RMII_RXER

- 85: PD5/LCD_D7/PWM_4/RMII_TXD1

- 86: PD6/LCD_D10/PWM_5/RMII_TXD0

- 87: PD7/LCD_D11/PWM_6/RMII_TXCK

- 88: PD8/LCD_D12/PWM_7/RMII_TXEN

3 NPU

V831的NPU是基于NVIDIA(英伟达)深度学习加速器(NVDLA)开源架构的定制来实现的

- NPU 时钟默认为 400 MHz,但可以设置在 100 到 1200 MHz 之间

- NPU 采用 nv_small 配置(NV 小型模型)实现,所有数据操作都依赖于共享系统内存。

- 支持 int8 和 int16,首选 int8 以提高速度和有限的板载内存(64Mb)

- 64 个 Mac (Atomic-C*Atomic-K)

- 可从用户空间编程的内存映射寄存器

- 当引用权重和输入/输出数据位置时,需要物理的地址,这意味如果从用户空间访问内核内存,则需要分配内核内存并检索物理地址。

- NPU 权重和输入/输出数据遵循与深度学习加速器(NVDLA)专用格式类似的布局,因此必须要先转换为 nhwc 或 nchw 等格式,然后再将其传送到 NPU。

4 Quick Start

V831 对应 sun8iw19p1 的代号

- https://cn.maixpy.sipeed.com/maixpy3/zh/install/maixii_m2dock/flash.html

- https://www.cnblogs.com/juwan/p/14336100.html

- V831/V833 的 SDK 的 kernel & package 的开发方法

5 Reference

- https://wiki.sipeed.com/hardware/zh/maixII/index.html

- https://dl.sipeed.com/shareURL/MaixII

- http://www.sochip.com.cn/v831/index.php?title=What_is_V831_%3F