ESP8266 特性

来自Jack's Lab

(版本间的差异)

(以“文件:esp8266ex-chip.jpg * 32-pin QFN 封装 * SDIO 2.0、SPI、UART 接口 * 集成 RF 开关、 balun、LNA、 24 dBm PA 、DCXO 和 电源管理单元(PMU...”为内容创建页面) |

|||

| 第1行: | 第1行: | ||

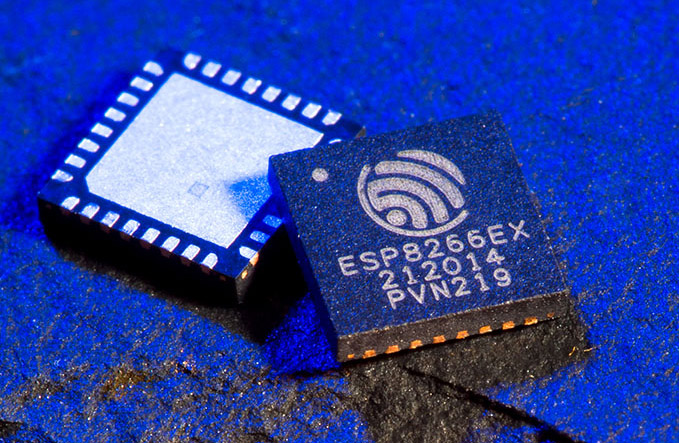

[[文件:esp8266ex-chip.jpg]] | [[文件:esp8266ex-chip.jpg]] | ||

| + | |||

* 32-pin QFN 封装 | * 32-pin QFN 封装 | ||

| 第16行: | 第17行: | ||

* 无需工厂的优化调试 | * 无需工厂的优化调试 | ||

* 外部无任何射频部件 | * 外部无任何射频部件 | ||

| + | |||

* 802.11 b/g/n | * 802.11 b/g/n | ||

2015年9月23日 (三) 14:34的版本

- 32-pin QFN 封装

- SDIO 2.0、SPI、UART 接口

- 集成 RF 开关、 balun、LNA、 24 dBm PA 、DCXO 和 电源管理单元(PMU)

- 集成 RISC 处理器、片上存储器和外部存储器接口

- 集成 MAC/基带处理器

- 高品质的服务管理

- 高保真音频应用所需的 I2S 接口

- 所有内部供电均包含片上低压差线性稳压器

- 专有的无杂散时钟生成架构

- 集成 WEP、 TKIP、AES 和 WAPI 引擎

- 射频部件具备自动校准功能,确保芯片在所有操作条件下都呈最佳表现

- 无需工厂的优化调试

- 外部无任何射频部件

- 802.11 b/g/n

- WiFi Direct (P2P)、soft-AP

- 集成 TCP/IP 协议栈

- 集成 TR 开关、 balun、LNA、 PA 和匹配网络

- 集成PLL、稳压器、DCXO 和电源管理单元

- 802.11b模式下 +19.5dBm 的输出功率

- 小于 10uA 的断电泄露电流

- 集成低功耗 32 位 CPU,可以兼作应用处理器

- SDIO 1.1/2.0、 SPI、UART 接口

- STBC、 1×1 MIMO、2×1 MIMO

- A-MPDU & A-MSDU 聚合 & 0.4ms 的保护间隔

- 2ms 之内唤醒并传递数据包

- 待机状态消耗功率少于 1.0mW (DTIM3)