Xtensa L106 Architecture

来自Jack's Lab

(版本间的差异)

(→See also) |

(→Overview) |

||

| 第14行: | 第14行: | ||

* 32-bit ALU | * 32-bit ALU | ||

* 16 GPRs | * 16 GPRs | ||

| + | |||

| + | <br><br> | ||

| + | |||

| + | == Xtensa ISA == | ||

| + | |||

| + | The Xtensa instruction set is designed to meet the diverse requirements of dataplane processing. | ||

| + | |||

| + | This 32-bit architecture features a compact 16- and 24-bit instruction set with modeless switching for maximum power efficiency and performance. | ||

| + | |||

| + | The base instruction set has 80 RISC instructions and includes a 32-bit ALU, up to 64 general-purpose 32-bit registers, and six special-purpose registers. | ||

| + | |||

| + | Using this instruction set, you can expect significant code size reductions that result in higher code density and better power dissipation. | ||

<br><br> | <br><br> | ||

2015年11月16日 (一) 17:41的版本

1 Overview

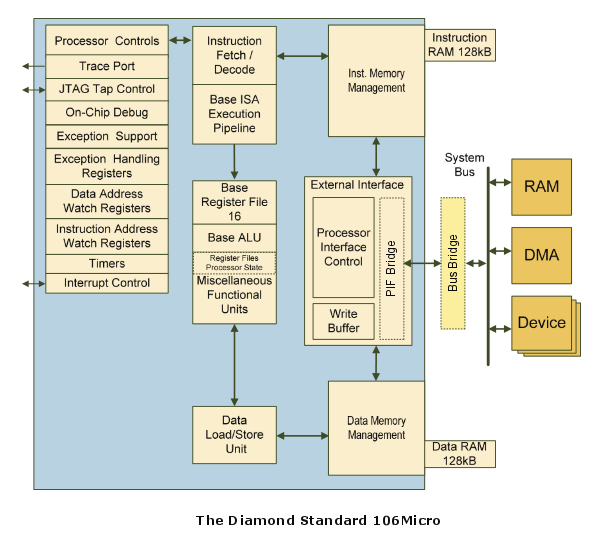

- Small, low power 32-bit RISC controller core, Xtensa ISA

- Cache-less processor with memory protection unit

- 5-stage pipeline

- Dhrystone 2.1: 1.22 DMIPS/MHz

- 24/16-bit ISA with modeless switching

- Iterative 32x32 multiplier

- Separate instruction and data memory interfaces

- Integrated interrupt controller with 15 interrupts at 2 priority levels

- 32-bit ALU

- 16 GPRs

2 Xtensa ISA

The Xtensa instruction set is designed to meet the diverse requirements of dataplane processing.

This 32-bit architecture features a compact 16- and 24-bit instruction set with modeless switching for maximum power efficiency and performance.

The base instruction set has 80 RISC instructions and includes a 32-bit ALU, up to 64 general-purpose 32-bit registers, and six special-purpose registers.

Using this instruction set, you can expect significant code size reductions that result in higher code density and better power dissipation.

3 See also

- Xtensa Instruction Set Architecture: http://0x04.net/~mwk/doc/xtensa.pdf

- Diamond Standard 106Micro Controller: http://ip.cadence.com/uploads/pdf/106Micro.pdf