航天器上的处理器

目录 |

1 概述

空间环境对电子信号的最大威胁就是电离辐射,其能使本来是 1 的数字信号“翻转”变成 0,反之亦然

因此航天处理器的主要性能指标就是抗辐射性、容错性,还有就是可靠、稳定

参考:南大西洋反常

2 SPARC

2.1 ERC32/LEON

ERC32 由欧洲航天局 (ESA) 设计,Temic(现被 Atmel 吞并)制造、销售。

有两个版本:

- 一个是ERC32 Chip Set,其由定点(TSC691E)、浮点(TSC692E) 和 Memory Controller (TSC693E) 三个芯片组成。现在 Atmel 已经不再生产,亦不再提供支持。

- 另一个是 ERC32 Single Chip (TSC695),定点、浮点和 Memory Controller 都做到一个芯片内。

其皆实现 SPARC V7 的指令集

后 ESA 重新设计了 ERC32,且将 VHDL 代码开源,先后实现了多个版本: LEON (SPARC V7),LEON2 (SPARC V8) 和最新的 LEON3 (SPARC V8)。

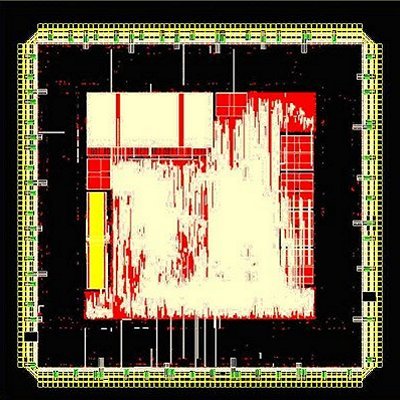

下图是 LEON2 的容错 (Fault Tolerant) 版本 -- LEON2FT:

嫦娥一号上主要的两台计算机即使用 ERC32(TSC695F)

参考:

LEON3-FT:

The LEON3FT is a fault-tolerant version of the standard LEON3 SPARC V8 Processor. It has been designed for operation in the harsh space environment, and includes functionality to detect and correct (SEU) errors in all on-chip RAM memories. The LEON3FT processor support most of the functionality in the standard LEON3 processor, and adds the following features:

- Register file SEU error-correction of up to 4 errors per 32-bit word

- Cache memory error-correction of up to 4 errors per tag or 32-bit word

- Autonomous and software transparent error handling

- No timing or performance impact due to error detection and correction

The following features of the standard LEON3 processor are NOT supported by LEON3FT

- Local scratch pad RAM (I and D)

- Cache locking

- LRR cache replacement algorithm

Fault-tolerance scheme

The fault-tolerance in LEON3FT is implemented using ECC coding of all on-chip RAM blocks. The ECC codes are adapted to the type of RAM blocks that are available for a given target technology, and to the type of data that is stored in the RAM blocks. The general scheme is to be able to detect and correct up to four errors per 32-bit RAM word. In RAM blocks where the data is mirrored in a secondary memory area (e.g. cache memories), the ECC codes are tuned for error-detection only. A correction cycle consists then of reloading the faulty data from the mirror location. In the cache memories, this equals to an invalidation of the faulty cache line and a cache line reload from main memory.

In RAM blocks where no secondary copy of the data is available (e.g. register file), the ECC codes are tuned for both error-detection and correction. The focus is placed on fast encoding/decoding times rather than minimizing the number of ECC bits. This approach ensures that the FT logic does not affect the timing and performance of the processor, and that LEON3FT can reach the same maximum frequency as the standard non-FT LEON3. The ECC encoding/decoding is done in the LEON3FT pipeline in parallel with normal operation, and a correction cycle is fully transparent to the software without affecting the instruction timing.

The ECC protection of RAM blocks is not limited to the LEON3FT processor. In a SOC design based on LEON3FT, any IP core using block RAM will have the RAM protected in a similar manner. This includes for instance the FIFOs in the SpaceWire IP core (GRSWP) and the buffer RAM in the CAN-2.0 IP core (CAN_OC).

Simulation and synthesis

The LEON3FT is simulated and synthesized in the same manner as the standard LEON3 processor. The area overhead for the FT logic is less than 15% on both ASIC and FPGA implementations. The table below shows some typical area figures for ASIC and RTAX technologies:

- http://en.wikipedia.org/wiki/ERC32

- http://www.esa.int/TEC/Microelectronics/

- http://www.atmel.com/dyn/products/devices.asp?family_id=641#1478

- http://www.gaisler.com/cms/index.php?option=com_content&task=section&id=4&Itemid=33

- https://www.gaisler.com/index.php/products/processors/leon3ft?task=view&id=194

2.2 EH32

3 MIPS

3.1 Mongoose-V

- Feature

Radiation hardened

10~15 MHz version of the MIPS R3000

Developed by Synova, Inc.

- Applications

- NASA's Earth Observer 1 (EO-1) satellite (launched in Nov. 2000) --- Main flight computer

- NASA's Microwave Anisotropy Probe (MAP), (launched in June 2001) --- Main flight computer similar to that on EO-1.

- NASA's three microsatellites of Space Technology 5 (ST5) (launched in Mar. 2006) --- Onboard flight computer (the Command & Data Handling system)

- NASA's New Horizons spacecraft --- Two computer system, the Command and Data Handling system and the Guidance and Control processor. Each of the two systems is duplicated for redundancy, giving a total of four computers.

- Reference

- [1] Speer, D. and G. Jackson and D. Raphael, "Flight Computer Design for the Space Technology 5 (ST-5) Mission," Proceedings of the 2002 IEEE Aerospace Conference, Big Sky, MT, March 2002.

- [3] http://www.synova.com/proc/mg5.html

- [4] http://en.wikipedia.org/wiki/Mongoose-V

- [5] http://en.wikipedia.org/wiki/New_Horizons#Flight_computer

3.2 RH32

- Feature

Radiation hardened, fault tolerance

Based on MIPS R3000

Manufactured by Honeywell

- Applications

- Reference

- [1] Hwang, A.S, "Radiation hardened 32-bit RISC microprocessor" Aerospace Conference Proceedings, 2000 IEEE, Big Sky, MT, 2000

- [2] http://www.honeywell.com/sites/aero/Data-Processing.htm

4 PowerPC

4.1 RHPPC

- Feature

Radiation hardened

Based on PowerPC 603e, compatible with the PowerPC architecture (Book I-III)

190MIPS @ 100MHz

25 ~ 50 MHz 60xbus (SYSCLK)

Superscalar, Out-of-order, 5 units (include a float point unit)

Manufactured by Honeywell

- Applications

- Reference

4.2 RAD600

4.3 RAD750

5 C51

MIL-STD-1750A

6 参考文献

- 基于LEON3的高可靠体系结构设计关键技术研究,2006

- 航天高可靠处理器容错设计与实现,2007