MIPS 体系结构相关文集汇编

(→外设及其他) |

|||

| (未显示1个用户的52个中间版本) | |||

| 第1行: | 第1行: | ||

| + | [[文件:Mips-arch-header.jpg]] | ||

| + | |||

| + | |||

本页汇总有 Jack Tan(谭大杰) 近年所撰写的与 MIPS 体系结构相关的文章,多数为技术总结。 | 本页汇总有 Jack Tan(谭大杰) 近年所撰写的与 MIPS 体系结构相关的文章,多数为技术总结。 | ||

| − | + | == 已发布的 PDF 文档 == | |

| − | + | [http://wiki.jackslab.org/images/Mips.linux.inter.pdf MIPS Linux 异常中断代码分析 文档,涵盖中断、系统调用部分,当前版本 2007-04-12] | |

| + | [http://wiki.jackslab.org/images/Mips.tlb.arch.pdf MIPS TLB 结构和代码分析 文档,涵盖 MIPS 存储管理,当前版本 2008-03-23] | ||

| − | [ | + | [http://wiki.jackslab.org/images/Mips.cache.arch.pdf MIPS Cache 结构和代码分析 文档,涵盖 MIPS Cache 的方方面面,2008-05-30] |

| − | |||

| + | [http://people.jackslab.org/comcat/mydoc/godson.intro.pdf 龙芯2E体系结构概述,当前版本 2007-03-16] | ||

| − | [ | + | [http://people.jackslab.org/comcat/mydoc/godson.asm.pdf 龙芯2E体系结构与汇编语言编程文档,当前版本 2007-03-28] |

| + | [http://people.jackslab.org/comcat/mydoc/godson.mmi.pdf 龙芯2E多媒体编程简述,当前版本 2007-04-05] | ||

| − | [ | + | [http://people.jackslab.org/comcat/mydoc/godson2e.mmi.pdf 龙芯2E多媒体指令分析、测试文档,当前版本 2007-04-05] |

| − | + | <br><br> | |

| + | == MIPS64 体系结构 == | ||

| − | [[ | + | [[64位多核 MIPS 异常和中断结构]] |

| − | + | [[64位多核 MIPS 异常和中断内核代码分析 (1)]] | |

| + | 64位多核 MIPS 存储管理结构 (TLB) | ||

| − | + | <br><br> | |

| − | 原文整理于 2009-08-31 19: | + | == Kernel Patch == |

| + | |||

| + | [http://people.jackslab.org/comcat/patch/patch-2.6.17-godson-comcat linux kernel 2.6.17 for godson patch 基于龙梦提供的2.6.14,2006-12-15] | ||

| + | |||

| + | [http://people.jackslab.org/comcat/patch/patch-2.6-dword-unaligned-access-comcat Supporting unaligned access in godson2 platform, 2007-05-15] | ||

| + | |||

| + | [http://people.jackslab.org/comcat/patch/patch-2.6.18-oprofile-comcat Supporting oprofile in godson2e platform 2007-05-25] | ||

| + | |||

| + | [http://people.jackslab.org/comcat/patch/patch-2.6.22-comcat-pgd_shift kernel patch for correct pgdir shift in 16K page size 2007-07-20] | ||

| + | |||

| + | <br><br> | ||

| + | |||

| + | == 典型多核MIPS == | ||

| + | |||

| + | === XLR732 === | ||

| + | |||

| + | XLR 系 RMI (Raza Microelectronics, Inc) 于 2005 年推出的多核多线程处理器,主要面向高端的通信和网络应用。 | ||

| + | |||

| + | 同样的,RMI,fabless 也。下图是 XLR 8 核版本 (XLR732/532) 的一个框图: | ||

| + | |||

| + | [[文件:Mips-xlp732-arch.png]] | ||

| + | |||

| + | XLR732 含 8 个 MIPS64 R1 的核, | ||

| + | |||

| + | 每核为单发射定序 10 级流水线 (Single In-order Issue),分支预测方面,其具有 2K 项的 G-share table 以及 8 项返回地址栈 (Return Address Stack), 实现 4 个硬件线程,且具有 64KB 的 L1 Cache (32KB D-Cache, 32KB I-Cache)。单核具有 64 个 TLB 项,可配置为每个线程各用 16 项,且互不干扰。 | ||

| + | |||

| + | <br><br> | ||

| + | |||

| + | === Tilera 64 === | ||

| + | |||

| + | Tile64 是由美国 Tilera 公司设计的 64 核的 MIPS。这个 Tilera 是一个 fabless。 | ||

| + | |||

| + | Tile64 瞄准通用和高端嵌入式领域,主要面向网络、视频和电信应用。第一代发布于 2007 年 8 月 | ||

| + | |||

| + | [[文件:Mips-tilera-arch.png]] | ||

| + | |||

| + | 64 个核通过片内 Mesh 网络 (Tilera's iMesh) 互联,各核皆通过自身的非阻塞 switch 连入 Mesh 网。Mesh 的互联带宽可达 31 Tbps | ||

| + | |||

| + | 与一般的多核 MIPS 实现不同, Tile64 的每个核都有 L2 Cache。 | ||

| + | |||

| + | 核内采用顺序 (In-order) 3 发射 (three-issue) 短流水线,实现 MIPS-derived VLIW 指令集。 | ||

| + | |||

| + | 整个性能可以到 443 billion operations per second (BOPS) | ||

| + | |||

| + | 片内还集成有 4 个 DDR2 控制器,2 个 10GbE XAUI MAC/PHY,2 个 4x PCI-E,2 个 GbE MAC,1 个 Flexible I/O 接口。 | ||

| + | |||

| + | I/O 的带宽能达到 50Gbps | ||

| + | |||

| + | 操作频率 500MHz ~ 866MHz。 | ||

| + | |||

| + | 700MHz 时所有核都跑有应用的情形下,功耗是 11 ~ 22W。这个有点牛 B 了,平均每个核的功耗是 0.34375W | ||

| + | |||

| + | |||

| + | ;ISA feature | ||

| + | |||

| + | Tilera ISA 面向 video 和 network 应用,可看作是 RISC 和 DSP 的混合体 | ||

| + | |||

| + | VLIW, 指令束长 64bit,最多可放 3 条指令 | ||

| + | |||

| + | ;64 个 32bit User Level Register: | ||

| + | |||

| + | <pre> | ||

| + | Register Name Purpose | ||

| + | r0-r52 General Purpose | ||

| + | tp Thread Pointer | ||

| + | sp Stack Pointer | ||

| + | lr Link Register | ||

| + | sn Static Network | ||

| + | io0-io1 IDN Ports 0-1 | ||

| + | us0-us3 UDN Ports 0-3 | ||

| + | zero Read As Zero | ||

| + | </pre> | ||

| + | |||

| + | |||

| + | <br><br> | ||

| + | |||

| + | == 相关分析、总结笔记 == | ||

| + | |||

| + | [[现代 CPU 中的 Cache 结构]] 原文2011-04-14发表于弯曲评论,现转移到 WIKI 里维护 | ||

| + | |||

| + | |||

| + | [[MIPS Linux 最初启动流程]] 原文整理于 2007-12-20 22:19,发表于个人的百度空间,现转移到 WIKI 里维护 | ||

| + | |||

| + | [[MIPS Linux SMP 启动流程]] 原文整理于 2007-12-27 22:44,发表于个人的百度空间 | ||

| + | |||

| + | [[MIPS Linux O32 之间接系统调用]] 原文整理于 2010-04-13 21:03,发表于个人的百度空间 | ||

| + | |||

| + | [[MIPS Linux 下添加系统调用 ]] 原文整理于 2007-09-06 09:57,发表于个人的CSDN空间 | ||

| + | |||

| + | |||

| + | [[MIPS Linux 上下文切换分析笔记]] 原文整理于 2008-01-10 21:26,发表于个人的CSDN空间 | ||

| + | |||

| + | [[MIPS Linux 存储管理分析札记]] 原文整理于 2008-01-10 21:25,发表于个人的CSDN空间 | ||

| + | |||

| + | [[MIPS 下非对其访问问题]] 原文整理于 2007-07-31 14:37,发表于个人的CSDN空间 | ||

| + | |||

| + | [[使用 oprofile 分析性能瓶颈]] 原文整理于 2007-09-06 10:31,发表于个人的CSDN空间 | ||

| + | |||

| + | |||

| + | [[MIPS Linux 内核页表隐性 Bug 分析与修复]] 原文整理于 2007-10-11 13:59,发表于个人的CSDN空间 | ||

| + | |||

| + | [[MIPS Linux PCI 调试技巧]] 原文整理于 2010-03-05 11:20,发表于个人的百度空间 | ||

| + | |||

| + | |||

| + | [[Using Watchpoints register to monitor momery access on MIPS]] 原文整理于 2007-12-20 23:23,发表于个人的百度空间 | ||

| + | |||

| + | [[Dump the MIPS TLB refill handler]] 原文整理于 2009-03-02 22:07,发表于个人的百度空间 | ||

| + | |||

| + | |||

| + | [[MIPS 缓冲区溢出]] 原文整理于 2009-08-31 19:56,发表于个人的百度空间 | ||

| 第34行: | 第150行: | ||

[[分支延迟槽]] | [[分支延迟槽]] | ||

| − | |||

| − | |||

| + | [[浮点标准 IEEE754 精要]] | ||

| − | [[ | + | [[内存容量自动识别]] |

| − | + | <br><br> | |

| + | == 外设及其他 == | ||

| + | [[UART 体系结构]] | ||

| − | + | [[PCI 结构概述]] | |

| − | [ | + | [[IA32 SSE3 精要]] |

| − | [ | + | [[ARM 内核crash示例]] |

| − | [ | + | [[MTD]] |

| + | |||

| + | [[Linux 下绑定进程到 CPU]] | ||

| + | [[终于让异构多核各跑了一个Linux]] | ||

| + | [[MIPS]] | ||

| − | + | <br><br> | |

| − | + | ||

| − | + | ||

| − | + | ||

2021年3月14日 (日) 07:50的最后版本

本页汇总有 Jack Tan(谭大杰) 近年所撰写的与 MIPS 体系结构相关的文章,多数为技术总结。

目录 |

[编辑] 1 已发布的 PDF 文档

MIPS Linux 异常中断代码分析 文档,涵盖中断、系统调用部分,当前版本 2007-04-12

MIPS TLB 结构和代码分析 文档,涵盖 MIPS 存储管理,当前版本 2008-03-23

MIPS Cache 结构和代码分析 文档,涵盖 MIPS Cache 的方方面面,2008-05-30

龙芯2E体系结构与汇编语言编程文档,当前版本 2007-03-28

龙芯2E多媒体指令分析、测试文档,当前版本 2007-04-05

[编辑] 2 MIPS64 体系结构

64位多核 MIPS 存储管理结构 (TLB)

[编辑] 3 Kernel Patch

linux kernel 2.6.17 for godson patch 基于龙梦提供的2.6.14,2006-12-15

Supporting unaligned access in godson2 platform, 2007-05-15

Supporting oprofile in godson2e platform 2007-05-25

kernel patch for correct pgdir shift in 16K page size 2007-07-20

[编辑] 4 典型多核MIPS

[编辑] 4.1 XLR732

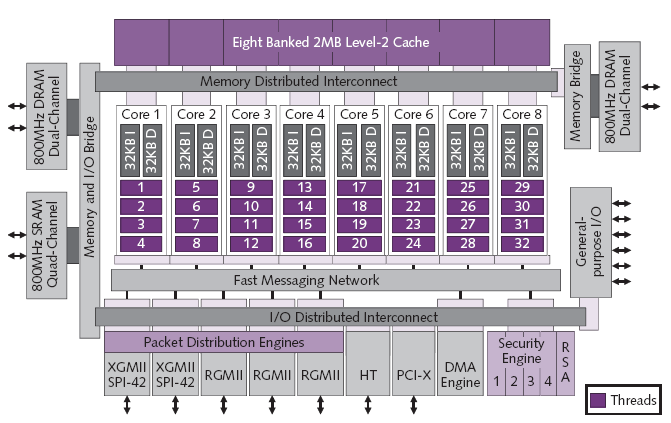

XLR 系 RMI (Raza Microelectronics, Inc) 于 2005 年推出的多核多线程处理器,主要面向高端的通信和网络应用。

同样的,RMI,fabless 也。下图是 XLR 8 核版本 (XLR732/532) 的一个框图:

XLR732 含 8 个 MIPS64 R1 的核,

每核为单发射定序 10 级流水线 (Single In-order Issue),分支预测方面,其具有 2K 项的 G-share table 以及 8 项返回地址栈 (Return Address Stack), 实现 4 个硬件线程,且具有 64KB 的 L1 Cache (32KB D-Cache, 32KB I-Cache)。单核具有 64 个 TLB 项,可配置为每个线程各用 16 项,且互不干扰。

[编辑] 4.2 Tilera 64

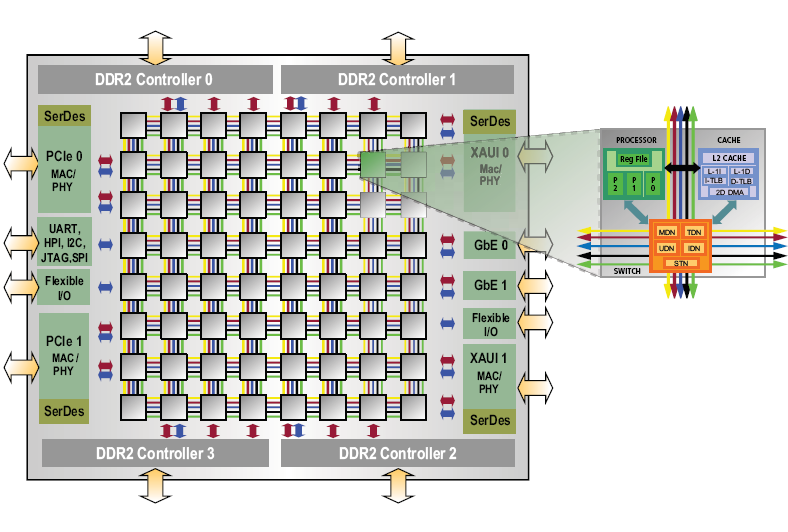

Tile64 是由美国 Tilera 公司设计的 64 核的 MIPS。这个 Tilera 是一个 fabless。

Tile64 瞄准通用和高端嵌入式领域,主要面向网络、视频和电信应用。第一代发布于 2007 年 8 月

64 个核通过片内 Mesh 网络 (Tilera's iMesh) 互联,各核皆通过自身的非阻塞 switch 连入 Mesh 网。Mesh 的互联带宽可达 31 Tbps

与一般的多核 MIPS 实现不同, Tile64 的每个核都有 L2 Cache。

核内采用顺序 (In-order) 3 发射 (three-issue) 短流水线,实现 MIPS-derived VLIW 指令集。

整个性能可以到 443 billion operations per second (BOPS)

片内还集成有 4 个 DDR2 控制器,2 个 10GbE XAUI MAC/PHY,2 个 4x PCI-E,2 个 GbE MAC,1 个 Flexible I/O 接口。

I/O 的带宽能达到 50Gbps

操作频率 500MHz ~ 866MHz。

700MHz 时所有核都跑有应用的情形下,功耗是 11 ~ 22W。这个有点牛 B 了,平均每个核的功耗是 0.34375W

- ISA feature

Tilera ISA 面向 video 和 network 应用,可看作是 RISC 和 DSP 的混合体

VLIW, 指令束长 64bit,最多可放 3 条指令

- 64 个 32bit User Level Register

Register Name Purpose r0-r52 General Purpose tp Thread Pointer sp Stack Pointer lr Link Register sn Static Network io0-io1 IDN Ports 0-1 us0-us3 UDN Ports 0-3 zero Read As Zero

[编辑] 5 相关分析、总结笔记

现代 CPU 中的 Cache 结构 原文2011-04-14发表于弯曲评论,现转移到 WIKI 里维护

MIPS Linux 最初启动流程 原文整理于 2007-12-20 22:19,发表于个人的百度空间,现转移到 WIKI 里维护

MIPS Linux SMP 启动流程 原文整理于 2007-12-27 22:44,发表于个人的百度空间

MIPS Linux O32 之间接系统调用 原文整理于 2010-04-13 21:03,发表于个人的百度空间

MIPS Linux 下添加系统调用 原文整理于 2007-09-06 09:57,发表于个人的CSDN空间

MIPS Linux 上下文切换分析笔记 原文整理于 2008-01-10 21:26,发表于个人的CSDN空间

MIPS Linux 存储管理分析札记 原文整理于 2008-01-10 21:25,发表于个人的CSDN空间

MIPS 下非对其访问问题 原文整理于 2007-07-31 14:37,发表于个人的CSDN空间

使用 oprofile 分析性能瓶颈 原文整理于 2007-09-06 10:31,发表于个人的CSDN空间

MIPS Linux 内核页表隐性 Bug 分析与修复 原文整理于 2007-10-11 13:59,发表于个人的CSDN空间

MIPS Linux PCI 调试技巧 原文整理于 2010-03-05 11:20,发表于个人的百度空间

Using Watchpoints register to monitor momery access on MIPS 原文整理于 2007-12-20 23:23,发表于个人的百度空间

Dump the MIPS TLB refill handler 原文整理于 2009-03-02 22:07,发表于个人的百度空间

MIPS 缓冲区溢出 原文整理于 2009-08-31 19:56,发表于个人的百度空间

[编辑] 6 外设及其他